Accueil > Recherche > Outils > Fast and Accurate TLM Simulations using Temporal Decoupling for FIFO-based (...)

Fast and Accurate TLM Simulations using Temporal Decoupling for FIFO-based Communications

The Smart FIFO

mercredi 27 mars 2013

A known approach to improve the timing accuracy of an untimed or loosely timed TLM model is to add timing annotations into the code and to reduce the number of costly context switches using temporal decoupling, meaning that a process can go ahead of the simulation time before synchronizing again.

The goal of that work was to apply temporal decoupling to the TLM platform of a heterogeneous many-core SoC dedicated to high performance computing, known as P2012 / STHORM. Part of this SoC communicates using classic memory-mapped buses, but it can be extended with hardware accelerators communicating using FIFOs. Whereas temporal decoupling for memory-based transactions has been widely studied, FIFO-based communications raise issues that have not been addressed before.

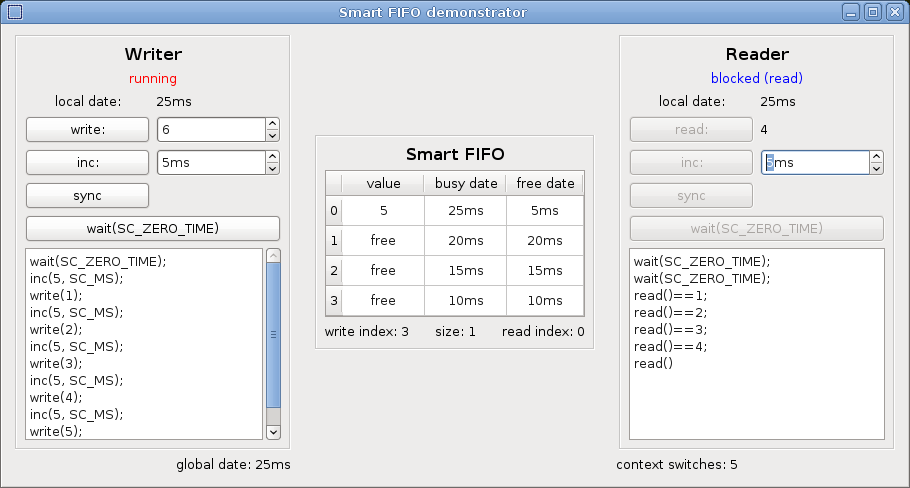

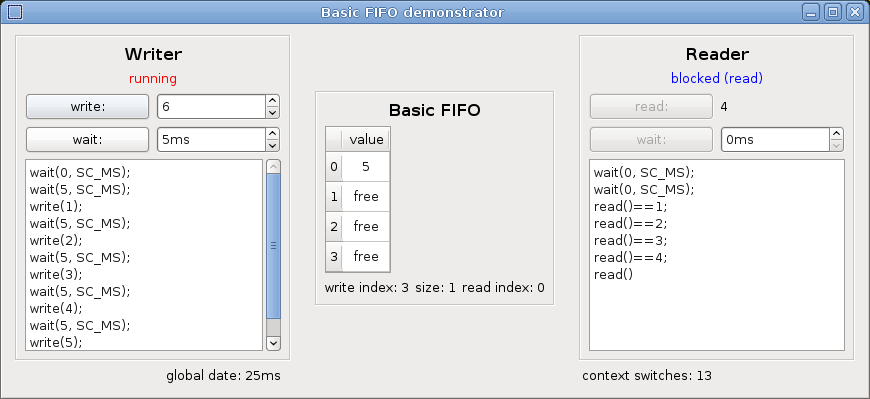

This paper and poster present an efficient solution to combine temporal decoupling and FIFO-based communications. Additionally, for demonstration purpose, we plugged a graphical interface on a small SystemC benchmark with one FIFO and two processes. One version uses the new Smart FIFO (screenshot 1) whereas a second version uses a basic FIFO without temporal decoupling (screenshot 2).

Authors :

– Claude Helmstetter, CEA-LETI (now at Verimag-CNRS)

– Jérôme Cornet, STMicroelectronics Grenoble

– Bruno Galilée, STMicroelectronics Grenoble

– Matthieu Moy, Verimag-Grenoble INP

– Pascal Vivet, CEA-LETI