#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

#### Hamza RIHANI

Thèse dirigée par **Matthieu MOY**, , Université Claude Bernard Lyon 1

préparée au sein du Laboratoire VERIMAG dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

## Analyse temporelle des systèmes tempsréels sur architectures pluri-coeurs

# **Many-Core Timing Analysis of Real-Time Systems**

Thèse soutenue publiquement le **1 décembre 2017**, devant le jury composé de :

#### **Monsieur MATTHIEU MOY**

MAITRE DE CONFERENCES, UNIVERSITE LYON 1, Directeur de thèse Madame CLAIRE MAÏZA

MAITRE DE CONFERENCES, GRENOBLE INP, Examinateur

#### **Madame CHRISTINE ROCHANGE**

PROFESSEUR, UNIVERSITE TOULOUSE-III-PAUL-SABATIER, Rapporteur

#### **Monsieur JAN REINEKE**

PROFESSEUR, UNIVERSITE DE LA SARRE - ALLEMAGNE, Rapporteur

#### **Monsieur ROBERT I DAVIS**

DIRECTEUR DE RECHERCHE, UNIVERSITE D'YORK - ROYAUME-UN, Président

#### Monsieur BENOÎT DUPONT DE DINECHIN

DIRECTEUR DE LA TECHNOLOGIE, KALRAY S.A. - MONTBONNOT-SAINT-MARTIN, Examinateur

# MANY-CORE TIMING ANALYSIS OF REAL-TIME SYSTEMS

and Its Application to an Industrial Processor

BY

#### HAMZA RIHANI

To obtain the academic degree of: Doctor of Philosophy in Computer Science

> Verimag Univ. Grenoble Alpes

Advisor: Dr. Matthieu Moy Supervisor: Dr. Claire Maïza

December 2017

This document is licensed under a Creative Commons Attribution 4.0 International (CC BY 4.0) license.

Hamza Rihani: Many-Core Timing Analysis of Real-Time Systems, © December 2017

#### ABSTRACT

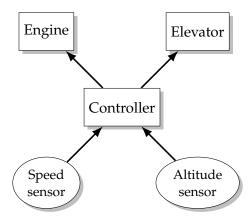

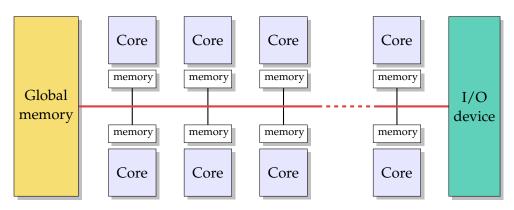

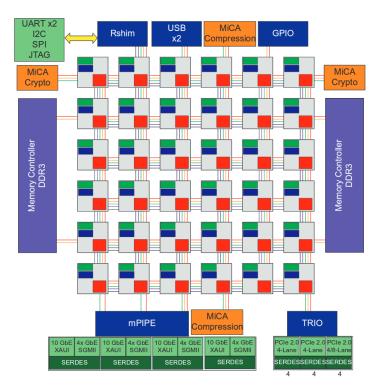

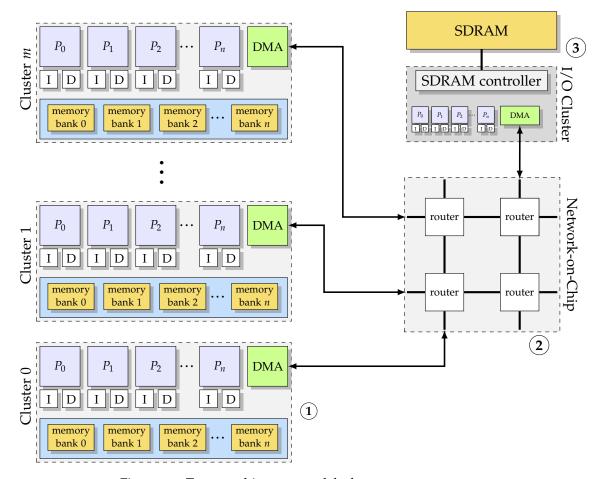

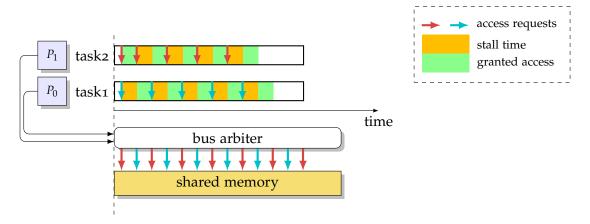

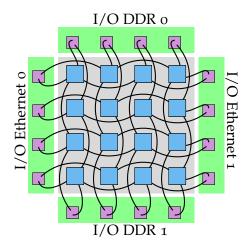

Predictability is of paramount importance in real-time and safety-critical systems, where non-functional properties – such as the timing behavior – have high impact on the system's correctness. As many safety-critical systems have a growing performance demand, classical architectures, such as single-cores, are not sufficient anymore. One increasingly popular solution is the use of multi-core systems, even in the real-time domain. Recent many-core architectures, such as the Kalray MPPA, were designed to take advantage of the performance benefits of a multi-core architecture while offering certain predictability. It is still hard, however, to predict the execution time due to interferences on shared resources (e.g., bus, memory, etc.).

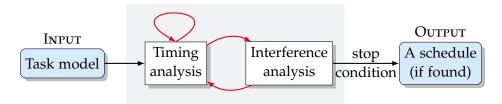

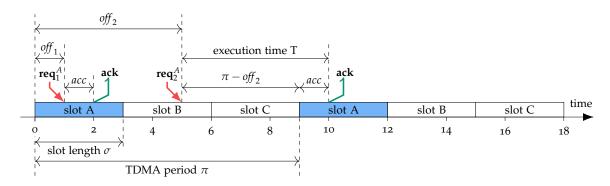

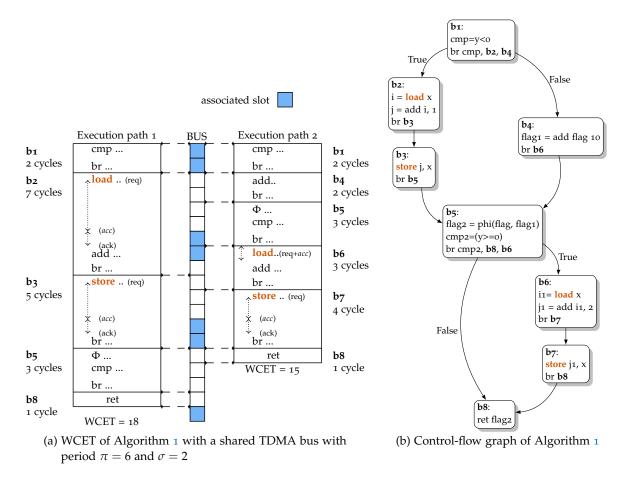

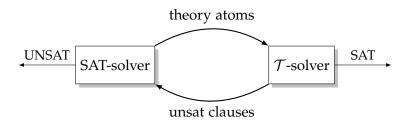

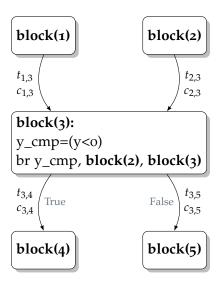

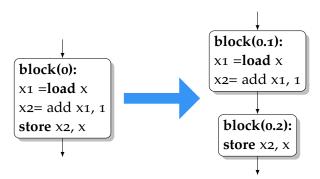

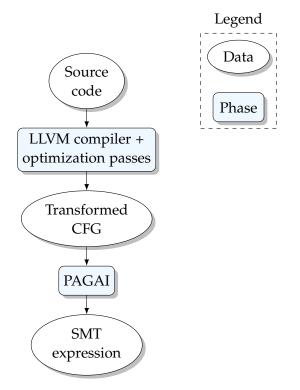

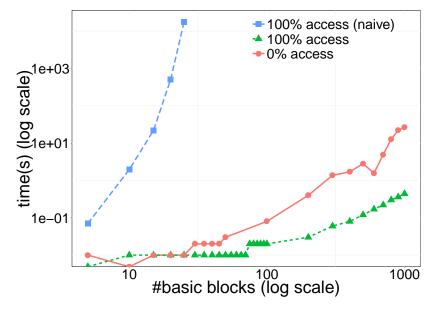

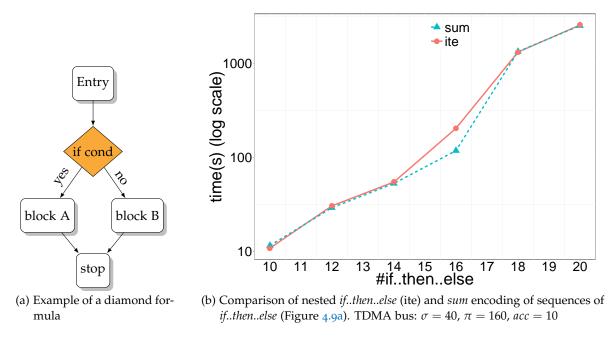

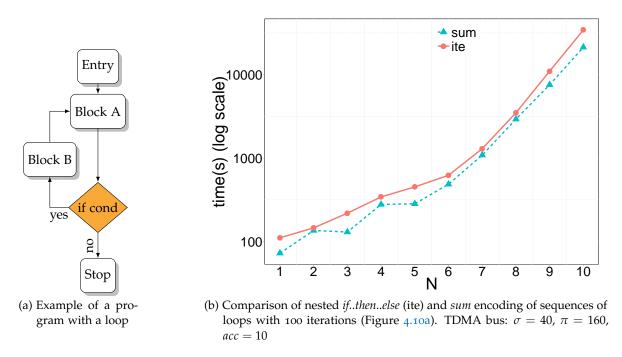

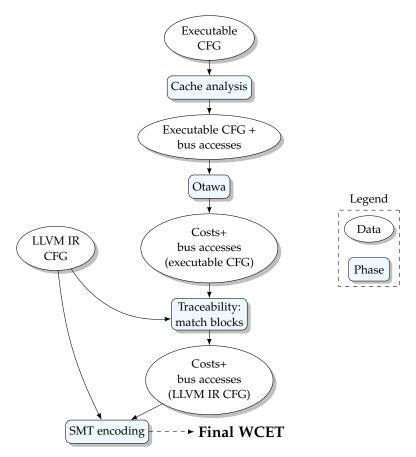

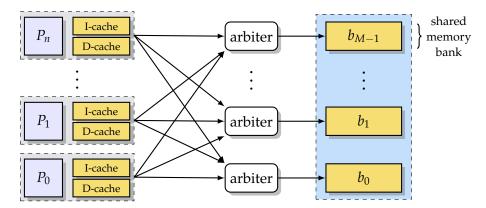

To tackle this challenge, Time Division Multiple Access (TDMA) buses are often advocated. In the first part of this thesis, we are interested in the timing analysis of accesses to shared resources in such environments. Our approach uses Satisfiability Modulo Theory (SMT) to encode the semantics and the execution time of the analyzed program. To estimate the delays of shared resource accesses, we propose an SMT model of a shared TDMA bus. An SMT-solver is used to find a solution that corresponds to the execution path with the maximal execution time. Using examples, we show how the worst-case execution time estimation is enhanced by combining the semantics and the shared bus analysis in SMT.

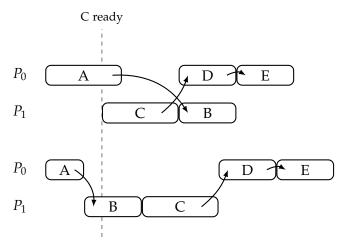

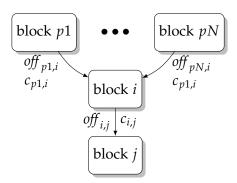

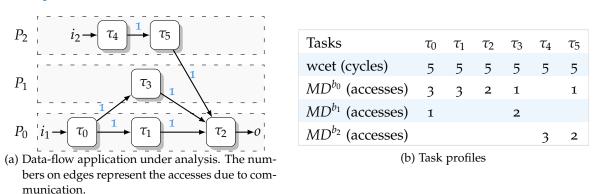

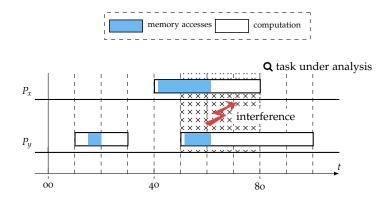

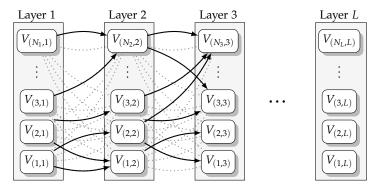

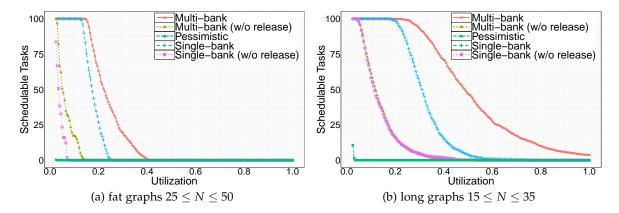

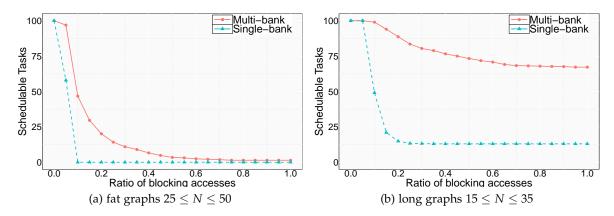

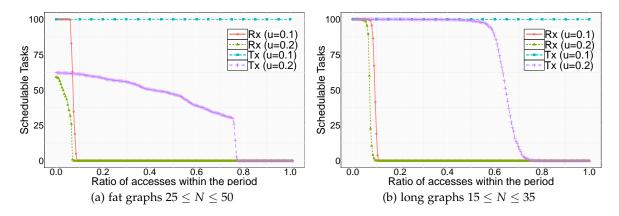

In the second part, we introduce a response time analysis technique for Synchronous Data Flow programs. These are mapped to multiple parallel dependent tasks running on a compute cluster of the Kalray MPPA-256 many-core processor. The analysis we devise computes a set of response times and release dates that respect the constraints in the task dependency graph. We derive a mathematical model of the multi-level bus arbitration policy used by the MPPA. Further, we refine the analysis to account for (i) release dates and response times of co-runners, (ii) task execution models, (iii) use of memory banks, (iv) memory accesses pipelining. Further improvements to the precision of the analysis were achieved by considering only accesses that block the emitting core in the interference analysis. Our experimental evaluation focuses on randomly generated benchmarks and an avionics case study.

**Keywords:** shared resource interference, many-core processors, worst-case execution time, response time, timing analysis, real-time systems.

### RÉSUMÉ

La prédictibilité est un aspect important des systèmes temps-réel critiques. Garantir la fonctionnalité de ces systèmes passe par la prise en compte des contraintes temporelles. Les architectures mono-cœurs traditionnelles ne sont plus suffisantes pour répondre aux besoins croissants en performance de ces systèmes. De nouvelles architectures multi-cœurs sont conçues pour offrir plus de performance mais introduisent d'autres défis. Dans cette thèse, nous nous intéressons au problème d'accès aux ressources partagées dans un environnement multi-cœur.

La première partie de ce travail propose une approche qui considère la modélisation de programme avec des formules de satisfiabilité modulo des théories (SMT). On utilise un solveur SMT pour trouver un chemin d'exécution qui maximise le temps d'exécution. On considère comme ressource partagée un bus utilisant une politique d'accès multiple à répartition dans le temps (TDMA). On explique comment la sémantique du programme analysé et le bus partagé peuvent être modélisés en SMT. Les résultats expérimentaux montrent une meilleure précision en comparaison à des approches simples et pessimistes.

Dans la deuxième partie, nous proposons une analyse de temps de réponse de programmes à flot de données synchrones s'exécutant sur un processeur pluri-cœur. Notre approche calcule l'ensemble des dates de début d'exécution et des temps de réponse en respectant la contrainte de dépendance entre les tâches. Ce travail est appliqué au processeur pluri-cœur industriel Kalray MPPA-256. Nous proposons un modèle mathématique de l'arbitre de bus implémenté sur le processeur. De plus, l'analyse de l'interférence sur le bus est raffinée en prenant en compte : (i) les temps de réponse et les dates de début des tâches concurrentes, (ii) le modèle d'exécution, (iii) les bancs mémoires, (iv) le *pipeline* des accès à la mémoire. L'évaluation expérimentale est réalisé sur des exemples générés aléatoirement et sur un cas d'étude d'un contrôleur de vol.

**Mots clés :** interférences sur ressources partagées, processeurs pluri-cœurs, temps de réponse, temps d'exécution pire-cas, analyse temporelle, système temps-réel.

#### **PUBLICATIONS**

Some ideas and figures have appeared previously in the following publications:

- [RMM16] Hamza Rihani, Claire Maiza, and Matthieu Moy. "Efficient Execution of Dependent Tasks on Many-Core Processors." In: *RTSOPS 2016*. 7th International Real-Time Scheduling Open Problems Seminar. Toulouse, France, July 2016.

- [Rih+15] Hamza Rihani, Matthieu Moy, Claire Maiza, and Sebastian Altmeyer. "WCET analysis in shared resources real-time systems with TDMA buses." In: *RTNS* 2015. 23rd International Conference on Real-Time Networks and Systems. Nov. 2015.

- [Rih+16] Hamza Rihani, Matthieu Moy, Claire Maiza, Robert I. Davis, and Sebastian Altmeyer. "Response Time Analysis of Synchronous Data Flow Programs on a Many-Core Processor." In: *Proceedings of the 24th International Conference on Real-Time Networks and Systems (RTNS)*. 2016, pp. 67–76.

#### **ACKNOWLEDGMENTS**

This thesis has been a journey of learning and self-improvement through hard work. The work presented here would not be possible without the participation of many people.

To my advisors Matthieu Moy and Claire Maïza who remind of what Stephen Covey wrote in his book: "Be a light, not a judge, be a model not a critic". They were a guiding light and inspiring models throughout my journey. I have an endless gratitude toward them for their trust and encouragement. They have been my mentors whom I look up to. Thanks to Matthieu for showing me that working with passion leads to higher quality results. He amazed me with his intelligence and brilliance in facing hard challenges. Thanks to Claire who knew how to motivate and push me when I needed it the most. Her vibrant energy and the synergy she brought in this work helped it to progress and result in interesting collaborations.

My gratitude goes to the jury members who took the time to evaluate my PhD thesis and for their decision to entitle me with the Doctor degree. I thank Christine Rochange, Jan Reineke, for reviewing the manuscript. Thanks to Benoît Dupont de Dinechin and Robert I. Davis for being examiners

This PhD thesis is funded by the grant *CAPACITES* from the french *Ministère de l'économie, des finances et de l'industrie*. I would like to thank all the partners and participants in this project; I had fruitful collaborations with Isabelle Puaut and Damien Hardy from IRISA, as well as Christine Rochange, Hugues Cassé, and Wei-Tsun Sun from IRIT. Many thanks to Benoît Dupont de Dinechin, CTO of Kalray, who was always available for discussions despite his busy schedule. Without the openness and transparency of Kalray, the work of this thesis would not have been possible. I would like to salute all the employees of Kalray who are always ready to help and to answer any request.

Special thanks go to all the people of the Real-Time Systems community whom I met during academic events. Thanks to my co-authors Sebastian Altmeyer and Robert I. Davis. The discussion we had during RTNS 2015 was a starting point of what gave a large part of the work presented in this thesis. Thanks to Sophie Quinton, Joël Goosens, Vincent Nélis, Jan Reineke, for the many meetings and insightful discussions we had.

Many thanks to the members of Verimag lab for all the formal and informal discussions and for simply being a part of this adventure. I was fortunate to be surrounded with wonderful and inspiring people. In particular, thanks to Florence Maraninchi and Nicolas Halbwachs, successive directors of Verimag, who warmly welcomed me in this family. Thanks to Oded Maler and his collection of interesting books. Thanks to David Monniaux and Julien Henry for their help with the tool PAGAI. Thanks to the administrative staff and the system administrators of Verimag whose support provides a good environment for efficient work.

Furthermore, thanks to my colleagues and friends: Denis Becker, my office mate with whom I shared the stress of writing, Amaury Graillat, Vera Shalaeva, Thomas Rubiano, Maxime Puys, Anaïs Durand, Alexandre Maréchal, Valentin Touzeau, Alexandre Rocca, Irini Mens, Hang Yu, Mahieddine Dellabani, Lotfi Mediouni, Laurent Lemke, and all the current and future doctors at Verimag with whom I shared lunches and coffee breaks.

My life long friends: Ismail, Amine, Sami, and Farouk. To whom I say thanks for always being there for me. It is rare to have such persons who can ignite enthusiasm and ambition back whenever it is needed.

To Yuliia, who shared the bitter and the sweet of this thesis. She proofread my chapters and motivated me throughout the writing process. I am endlessly grateful to her.

Finally, to my parents, my sister, and my brothers, for all their unconditional love and support. Without them, I would not be who I am today.

## CONTENTS

| 1 | INT | RODUCTION                                                 | 1  |

|---|-----|-----------------------------------------------------------|----|

| 1 |     | Context and Motivation                                    |    |

|   | 1.1 |                                                           | 1  |

|   | 1.2 | Summary of Contributions                                  | 3  |

|   | 1.3 | Thesis Outline                                            | 4  |

| Ι | STA | ATE-OF-THE-ART                                            | 5  |

| 2 | BAC | CKGROUND                                                  | 7  |

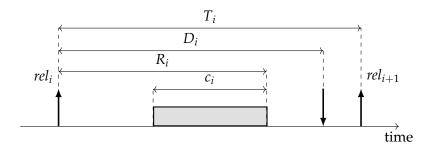

|   | 2.1 | Real-Time Systems                                         | 7  |

|   |     | 2.1.1 Requirements                                        | 9  |

|   |     | 2.1.2 Challenges in the Verification of Real-Time Systems | 10 |

|   | 2.2 | 11                                                        | 12 |

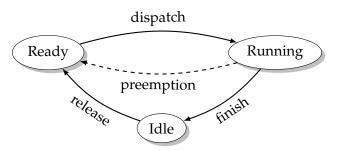

|   |     | 2.2.1 Task Models                                         | 12 |

|   |     | 2.2.2 Synchronous and Asynchronous Task Models            | 13 |

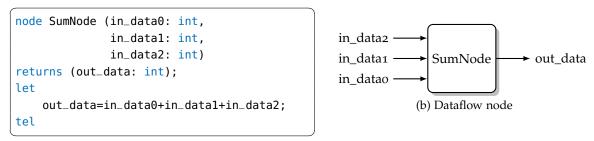

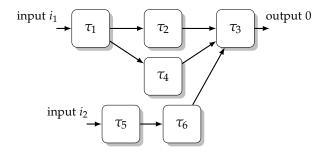

|   |     | 2.2.3 Synchronous Data-Flow Model                         | 14 |

|   |     | 2.2.4 Task Scheduling                                     | 15 |

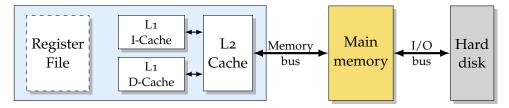

|   | 2.3 | Hardware Architectures                                    | 15 |

|   |     | 2.3.1 Multi-core and Many-core Architectures              | 16 |

|   |     | 2.3.2 Timing Compositionality                             | 17 |

|   |     | 2.3.3 Predictable Multi-core and Many-core Architectures  | 19 |

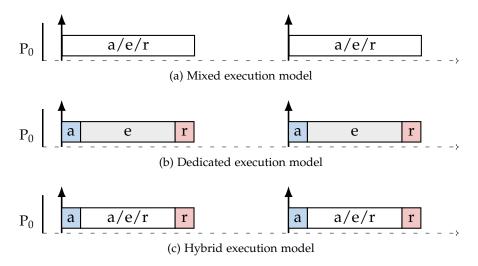

|   | 2.4 | Execution Models                                          | 21 |

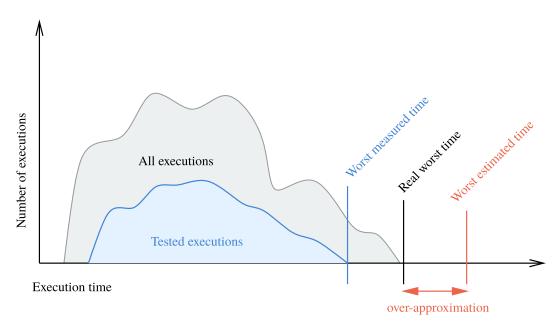

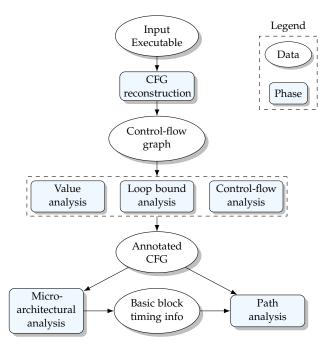

|   | 2.5 | Static Timing Analysis                                    | 22 |

|   |     | 2.5.1 Micro-architectural Analysis                        | 23 |

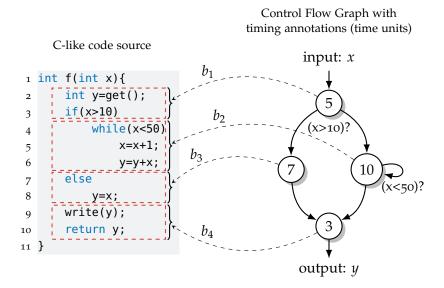

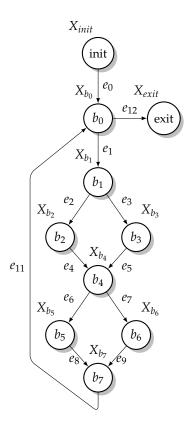

|   |     | 2.5.2 Path Analysis                                       | 24 |

|   |     | 2.5.3 Some WCET Tools                                     | 25 |

|   | 2.6 | Context of the Thesis                                     | 26 |

|   |     | 2.6.1 Time Division Multiplexing                          | 26 |

|   |     |                                                           | 26 |

| 3 | REL |                                                           | 29 |

|   | 3.1 |                                                           | 29 |

|   |     |                                                           | 31 |

|   |     |                                                           | 32 |

|   |     | mm                                                        | 33 |

|   |     |                                                           | 34 |

|   | 3.2 |                                                           | 34 |

|   | J   |                                                           | 34 |

|   |     |                                                           | 36 |

|   |     |                                                           | 37 |

|   | 3.3 |                                                           | 37 |

|   |     | T 1.4                                                     | 37 |

|   |     |                                                           | 39 |

|   |     | 3.3.3  | Summary                                                | 39         |

|---|-----|--------|--------------------------------------------------------|------------|

|   | 3.4 | Concl  | usion and Positioning                                  | 40         |

|   |     | 3.4.1  | On TDMA-based Buses                                    | 40         |

|   |     | 3.4.2  | On Shared Resources Interference                       | 40         |

| П | CO  | AITDID | UTIONS                                                 | 42         |

|   |     |        |                                                        | 43<br>45   |

| 4 |     |        |                                                        | 45<br>45   |

|   | 4.1 |        |                                                        | 45<br>     |

|   | 4.2 |        |                                                        | 47<br>47   |

|   |     | 4.2.1  |                                                        | 47         |

|   |     | 4.2.2  | •                                                      | 48         |

|   |     | 4.2.3  |                                                        | <b>49</b>  |

|   |     | 4.2.4  |                                                        | 51         |

|   | 4.3 |        |                                                        | 53         |

|   |     | 4.3.1  |                                                        | 53         |

|   |     | 4.3.2  | -                                                      | 54         |

|   |     | 4.3.3  |                                                        | 58         |

|   | 4.4 |        | ·                                                      | 58         |

|   |     | 4.4.1  | O                                                      | 60         |

|   |     | 4.4.2  |                                                        | 62         |

|   | 4.5 | Concl  |                                                        | 65         |

|   |     | 4.5.1  | ·                                                      | 65         |

|   |     | 4.5.2  |                                                        | 67         |

|   |     | 4.5.3  | Discussion                                             | 67         |

| 5 | RES |        |                                                        | 69         |

|   | 5.1 | Data-  | 11                                                     | 69         |

|   |     | 5.1.1  | ·                                                      | <b>7</b> 0 |

|   |     | 5.1.2  | •                                                      | 70         |

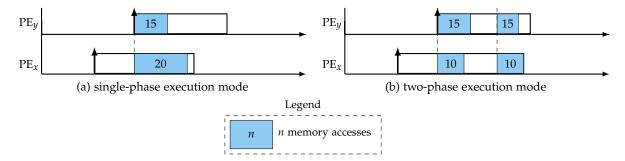

|   |     | 5.1.3  | Phase-based Execution Model                            | 72         |

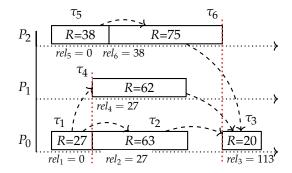

|   | 5.2 | Respo  | onse Time Analysis                                     | 72         |

|   |     | 5.2.1  |                                                        | 72         |

|   |     | 5.2.2  |                                                        | 74         |

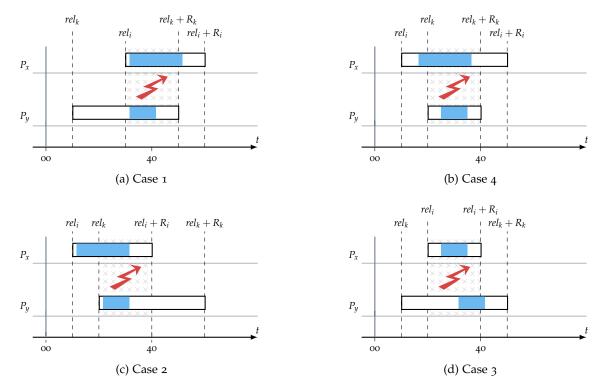

|   | 5.3 | Termi  | nation and Correctness of the Response Time Analysis   | 76         |

|   |     | 5.3.1  | Basic Properties of the Response Time Analysis         | 77         |

|   |     | 5.3.2  | Convergence of the Fixed-Point                         | 80         |

|   |     | 5.3.3  | Uniqueness of the Fixed-Point                          | 82         |

|   | 5.4 | Concl  | usion                                                  | 83         |

| 6 | SHA | RED R  | ESOURCE INTERFERENCE ANALYSIS ON A MANY-CORE PROCESSOR | 85         |

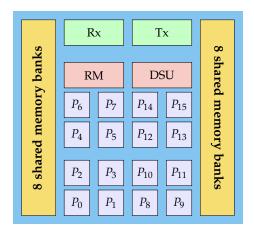

|   | 6.1 | Preser | ntation of the Kalray MPPA-256 Bostan                  | 85         |

|   |     | 6.1.1  | •                                                      | 86         |

|   |     | 6.1.2  |                                                        | 86         |

|   |     | 6.1.3  | ·                                                      | 87         |

|   | 6.2 | _      |                                                        | ,<br>88    |

|   | 6.3 |        |                                                        | 89         |

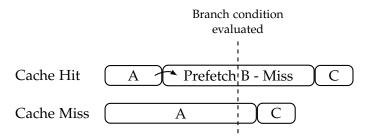

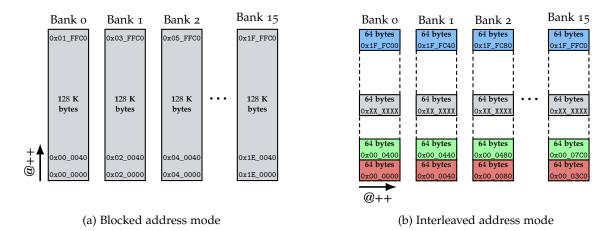

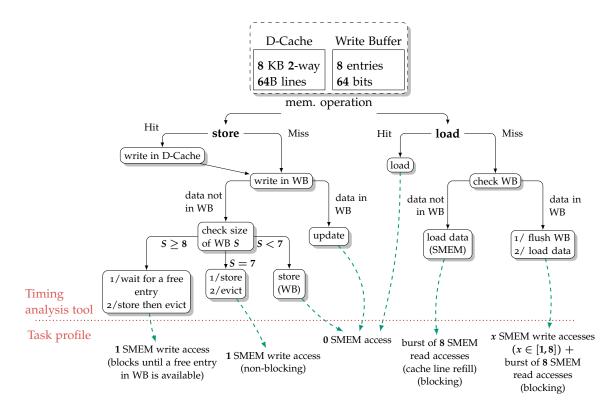

|     |     | 6.3.1  | Understanding Memory Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89  |

|-----|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

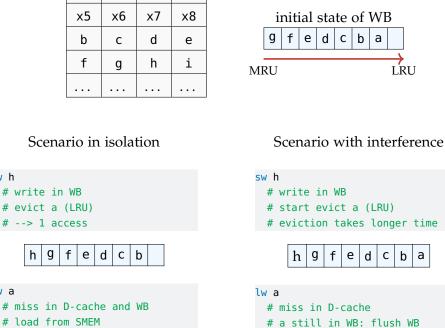

|     |     | 6.3.2  | Illustrative Examples on Cached Load and Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91  |

|     |     | 6.3.3  | Variables in Bus Interference Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92  |

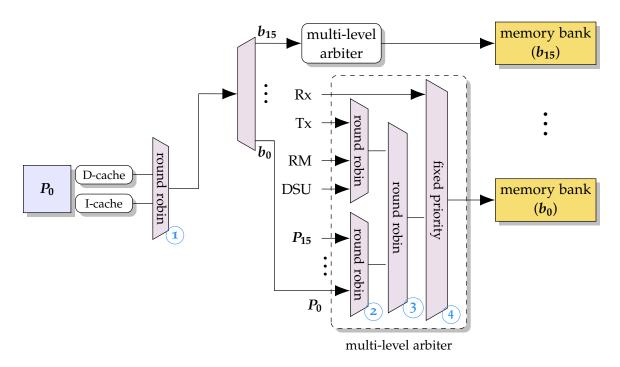

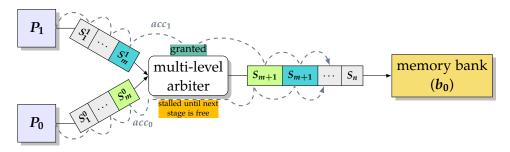

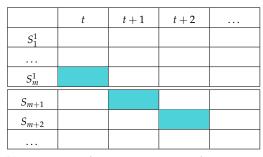

|     | 6.4 | Simpli | fied Model of the Multi-level Bus Arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93  |

|     | 6.5 | Full M | lodel of the Interference on Shared Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95  |

|     |     | 6.5.1  | Bursts of Memory Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95  |

|     |     | 6.5.2  | Memory Access Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96  |

|     |     | 6.5.3  | Blocking and Non-blocking Memory Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 97  |

|     |     | 6.5.4  | Arbitration Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97  |

|     | 6.6 | Timing | g Compositionality of Shared Resource Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

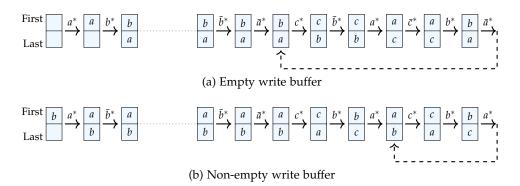

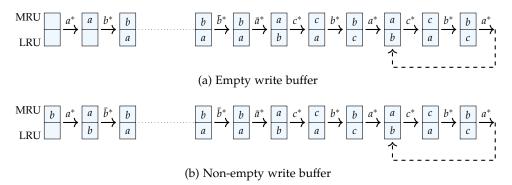

|     |     | 6.6.1  | Left Side and Right Side Bus Masters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99  |

|     |     | 6.6.2  | Write Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 |

|     | 6.7 | Conclu | asion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 103 |

|     |     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| III | EVA | ALUATI | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105 |

| 7   | EXP |        | NTAL EVALUATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 107 |

|     | 7.1 | -      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 107 |

|     |     | 7.1.1  | Bus Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 108 |

|     |     | 7.1.2  | Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 108 |

|     |     | 7.1.3  | Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 109 |

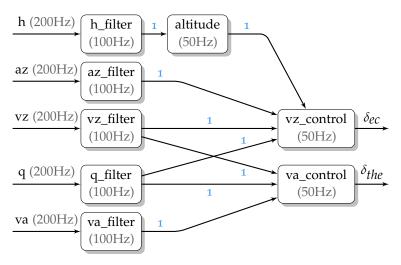

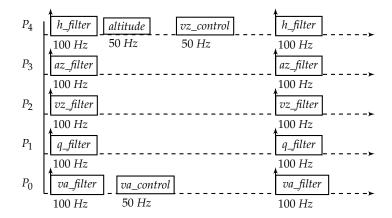

|     | 7.2 |        | tic Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110 |

|     | 7.3 | Rando  | y and the second | 111 |

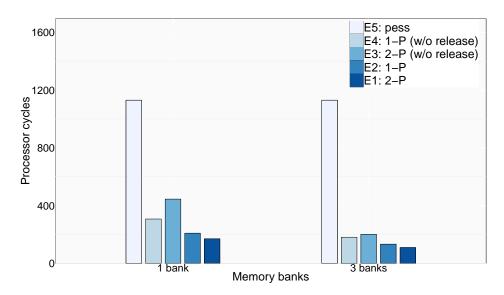

|     |     | 7.3.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 112 |

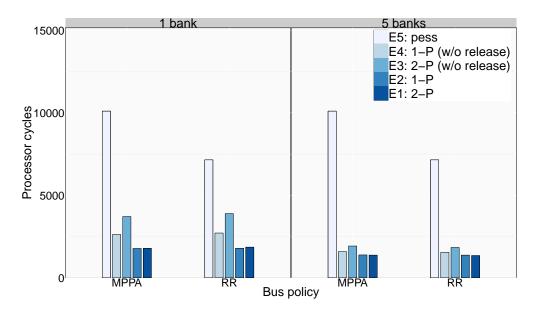

|     |     | 7.3.2  | e e e e e e e e e e e e e e e e e e e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113 |

|     |     | 7.3.3  | Effect of the Network-on-Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114 |

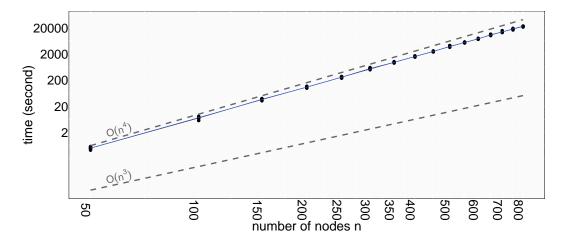

|     |     | 7.3.4  | Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 115 |

|     | 7.4 |        | , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 116 |

|     | 7.5 |        | asion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 118 |

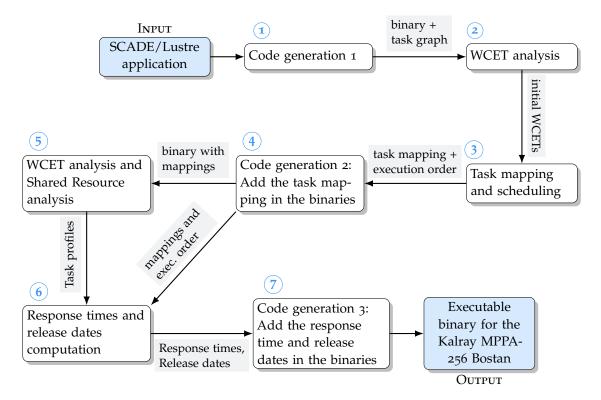

| 8   | FRO |        | ING ANALYSIS TO REAL-TIME IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121 |