# Communauté UNIVERSITÉ Grenoble Alpes

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

# Amaury GRAILLAT

Thèse dirigée par **Pascal RAYMOND** et codirigée par **Matthieu MOY**, Université Claude Bernard Lyon 1 préparée au sein du **Laboratoire VERIMAG** dans **l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique**

# Génération de code pour un many-core avec des contraintes temps réel fortes

# **Code Generation for Multi-Core Processor** with Hard Real-Time Constraints

Thèse soutenue publiquement le **16 novembre 2018**, devant le jury composé de :

# Monsieur PASCAL RAYMOND

CHARGE DE RECHERCHE, CNRS DELEGATION ALPES, Directeur de thèse **Monsieur MATTHIEU MOY** MAITRE DE CONFERENCES, UNIVERSITE LYON 1, Co-directeur de thèse Monsieur JAN REINEKE PROFESSEUR, UNIVERSITE DE LA SARRE - ALLEMAGNE, Rapporteur Monsieur ROBERT DE SIMONE DIRECTEUR DE RECHERCHE, INRIA CENTRE S, ANTIPOLIS -MEDITERRANEE, Rapporteur Madame ANNE BOUILLARD MAITRE DE CONFERENCES, ECOLE NORMALE SUPERIEURE DE PARIS, Examinateur Monsieur BENOÎT DUPONT DE DINECHIN INGENIEUR DE RECHERCHE, KALRAY S.A. - MONTBONNOT SAINT-MARTIN, Examinateur Monsieur ALAIN GIRAULT DIRECTEUR DE RECHERCHE, INRIA CENTRE DE GRENOBLE RHÔNE-ALPES, Président Madame CHRISTINE ROCHANGE PROFESSEUR, UNIVERSITE TOULOUSE-IIIIII PAUL-SABATIER, Examinateur

# Contents

| 1 | Rés        | sumé                                                                          | 9               |

|---|------------|-------------------------------------------------------------------------------|-----------------|

|   | 1.1        | Introduction                                                                  | 9               |

|   |            | 1.1.1 Applications temps-réel dur                                             | 9               |

|   |            | 1.1.2 L'impact des évolutions matérielles sur les logiciels temps-réel        | 9               |

|   |            | 1.1.3 L'usage des multi- et pluri-cœurs pour des applications critiques       | 10              |

|   |            | 1.1.4 La programmation par modèle et les langages synchrones                  | 11              |

|   |            | 1.1.5 Résumé des contributions : les programmes synchrones temps-réel dur sur |                 |

|   |            | pluri-cœur                                                                    | 11              |

|   | 1.2        | Méthode générale                                                              | 11              |

|   |            | 1.2.1 Définition de la Représentation Intermédiaire Parallèle                 | 12              |

|   |            | 1.2.2 Extraction des tâches parallèles                                        | 12              |

|   |            | 1.2.3 Choix d'implémentations pour tirer parti des bancs mémoire              | 12              |

|   |            | 1.2.4 Implémentation du PIR sur un pluri-cœur                                 | 13              |

|   | 1.3        | Conclusion                                                                    | 14              |

| 2 | Intr       | roduction                                                                     | 15              |

|   | 2.1        | Hard-Real-Time Applications                                                   | 15              |

|   | 2.2        | Impact of Hardware Evolution on Time-Critical Software                        | 15              |

|   |            | 2.2.1 Single-Core                                                             | 15              |

|   |            | 2.2.2 Single-Core vs. Multi-/Many-Core                                        | 15              |

|   |            | 2.2.3 Multi-/Many-Core for Time-Critical Applications                         | 16              |

|   | 2.3        | Model-Based Development and Synchronous Languages                             | 17              |

|   | 2.4        | Contributions Overview: Time-Critical Synchronous Program on a Many-core      | 17              |

|   | 2.5        | Organization of This Document                                                 | 17              |

| 3 | Bac        | kground: Synchronous Programs & Parallelization                               | 19              |

| J | 3.1        | Reactive Systems and Synchronous Languages                                    | <b>19</b>       |

|   | 0.1        | 3.1.1 The Core Language: Lustre                                               | $19 \\ 21$      |

|   |            | 3.1.2 Conditional Computation in Synchronous Data-Flow Languages              | $\frac{21}{22}$ |

|   |            | 3.1.2.1 Clocks in Lustre                                                      | $\frac{22}{22}$ |

|   |            | 3.1.2.1 Clocks in Lustre                                                      | $\frac{22}{24}$ |

|   |            | 3.1.3 Multi-Periodic Programs                                                 | $\frac{24}{25}$ |

|   |            | 3.1.3.1 Task Activation                                                       | $\frac{25}{25}$ |

|   |            | 3.1.3.2 Determinism of Communication                                          | $\frac{25}{27}$ |

|   |            | 3.1.4 Conclusion                                                              | 21<br>29        |

|   | <u>า</u> า |                                                                               | 29<br>29        |

|   | 3.2        | High-Level Parallel Design                                                    | 29<br>29        |

|   |            | 3.2.1       Existing Approaches for Parallelism         3.2.1.1       Prelude | 29<br>29        |

|   |            |                                                                               |                 |

|   |            |                                                                               | 30              |

|   |            | 3.2.1.3 Giotto / Timing Definition Language (TDL)                             | 30              |

# CONTENTS

|   |     |        | 3.2.1.4ARINC 653333.2.1.5Architecture Analysis and Design Language (AADL)34 |   |

|---|-----|--------|-----------------------------------------------------------------------------|---|

|   |     |        | 3.2.1.6 Conclusion                                                          | ŀ |

|   |     | 3.2.2  | Parallelization from Synchronous Languages                                  | ŀ |

|   |     |        | 3.2.2.1 Parallel Scade                                                      | ŀ |

|   |     |        | 3.2.2.2 Distributed Lustre                                                  | ý |

|   |     |        | 3.2.2.3 Other Languages                                                     | ý |

|   |     |        | 3.2.2.4 Parallelization of Dataflow                                         | ý |

|   |     |        | 3.2.2.5 Conclusion                                                          | j |

| 4 | Bac | karow  | nd: Many-Core 37                                                            | 7 |

| 4 | 4.1 | -      | and Many-Cores System-on-Chip Architectures                                 |   |

|   | 4.1 | 4.1.1  |                                                                             |   |

|   |     | 4.1.1  | 4.1.1.1 WCET in Isolation                                                   |   |

|   |     |        | 4.1.1.2 Interference-Aware WCET Analysis                                    |   |

|   |     | 4.1.2  | System-on-Chip For Time-Critical Software                                   |   |

|   |     | 4.1.2  | System-on-Chip For Time-Critical Software                                   |   |

|   |     | 4.1.0  | 4.1.3.1 DRAM Overview                                                       |   |

|   |     |        | 4.1.3.2 Memory Organization: Rank / Bank / Row / Column                     |   |

|   |     |        | 4.1.3.3 Temporal Behavior                                                   |   |

|   |     |        | 4.1.3.4 Timing Predictability with SDRAM                                    |   |

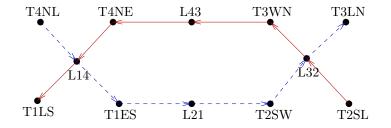

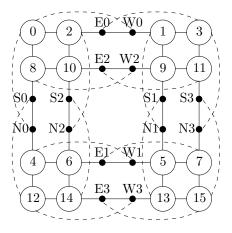

|   | 4.2 | Netwo  | rk-on-Chip                                                                  |   |

|   | 1.4 | 4.2.1  | Definitions                                                                 |   |

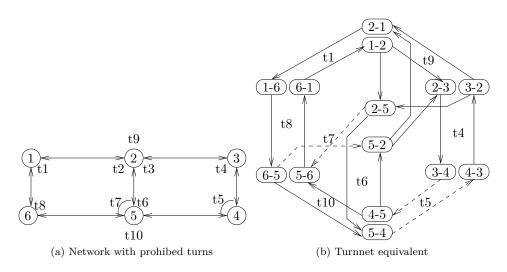

|   |     | 4.2.2  | Routing and Deadlock                                                        |   |

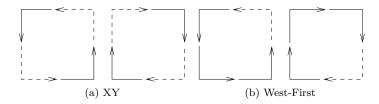

|   |     | 4.2.3  | Adaptive Routing                                                            |   |

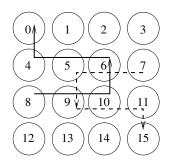

|   |     | 4.2.4  | 2D Grid Deadlock-Free Routing Algorithms                                    |   |

|   |     | 4.2.5  | Bandwidth Limiter                                                           |   |

|   |     | 4.2.6  | Max-Min Fairness and Lexicographic Vector                                   |   |

|   |     | 4.2.7  | Network Calculus                                                            |   |

|   |     | 4.2.8  | Classical Artificial Instances of Flows                                     |   |

|   | 4.3 |        | Calray MPPA2       59                                                       |   |

|   | 1.0 | 4.3.1  | Cores                                                                       |   |

|   |     | 1.0.1  | 4.3.1.1 VLIW vs. Out of Order Pipeline                                      |   |

|   |     |        | 4.3.1.2 Caches                                                              |   |

|   |     | 4.3.2  | Cluster                                                                     |   |

|   |     | 1.0.2  | 4.3.2.1 Shared-Memory                                                       |   |

|   |     |        | 4.3.2.2 Input/Output Clusters                                               |   |

|   |     |        | 4.3.2.3 Clocks and Synchronizations Mechanisms                              |   |

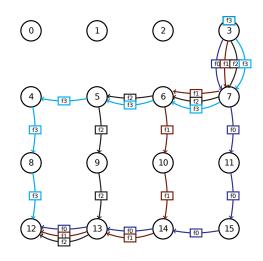

|   |     | 4.3.3  | Network-on-Chip                                                             |   |

|   |     | 4.3.4  | Summary of the Kalray MPPA2 Features                                        |   |

| 5 | Met | thod C | overview 65                                                                 | ( |

| 0 | 5.1 |        | el Intermediate Representation Definition                                   |   |

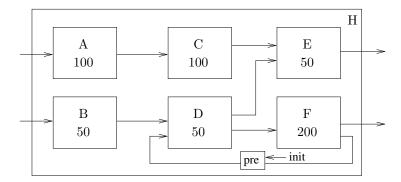

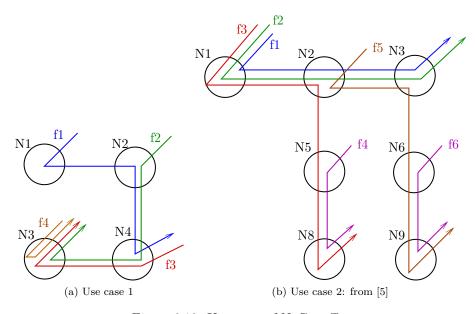

|   | 0.1 | 5.1.1  | Task Graph and Communication Graph   65                                     |   |

|   | 5.2 | -      | Program to PIR: Task Extraction                                             |   |

|   | 5.3 |        | nentation Choices to Take Advantage of the Banked Shared-Memory             |   |

|   | 0.0 | 5.3.1  | Inter-Task Communications: Remote Read vs. Remote Write                     |   |

|   |     | 5.3.2  | Time-Triggered Execution Model                                              |   |

|   | 5.4 |        | nentation of a PIR on a Many-Core                                           |   |

|   | 0.1 | 5.4.1  | Static Mapping-Scheduling                                                   |   |

|   |     | 5.4.2  | Release Dates and Final Executable                                          |   |

|   |     | 5.4.3  | NoC: Routes and WCTT                                                        |   |

|   |     |        |                                                                             |   |

|   | 5.5   | The CAPACITES Project                                                                                          |

|---|-------|----------------------------------------------------------------------------------------------------------------|

|   | 5.6   | Conclusion                                                                                                     |

| 0 | ъ     |                                                                                                                |

| 6 |       | vallelization of Synchronous Programs       7         Main Criteria to Select a Parallelization Method       7 |

|   | 6.1   |                                                                                                                |

|   |       |                                                                                                                |

|   |       | 6.1.2 Hierarchical Parallelism Extraction                                                                      |

|   |       | 6.1.3 Code Traceability                                                                                        |

|   | 0.0   | 6.1.4 Special Case for Clocks and Delayed Communications                                                       |

|   | 6.2   | Parallelization of Lustre and Scade                                                                            |

|   |       | 6.2.1 Fork-Join for Dataflow Synchronous Languages                                                             |

|   |       | 6.2.2 Decoupling of the Nodes Using Future in Lustre                                                           |

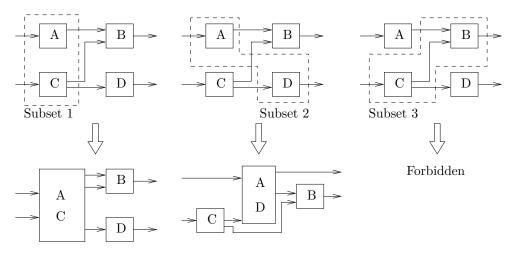

|   |       | 6.2.3 Parallel Subset in Scade                                                                                 |

|   |       | 6.2.4 Top-Level Node as an Architecture Description Language                                                   |

|   |       | 6.2.5 Data-Flow Flattening                                                                                     |

|   |       | 6.2.6 Methods Comparison                                                                                       |

|   | 6.3   | Contribution: Extraction of PIR from a Dataflow Synchronous Program                                            |

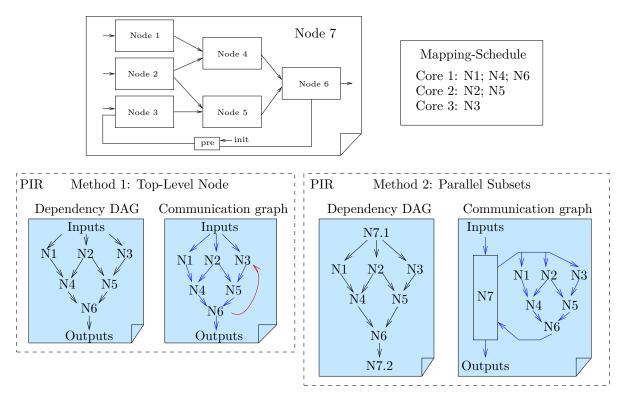

|   |       | 6.3.1 Parallelization Method 1: Lustre Top-Level                                                               |

|   |       | 6.3.2 Parallelization Method 2: Parallel Subsets from KCG Multi-Core                                           |

|   |       | 6.3.2.1 Simple Data-Flow Program                                                                               |

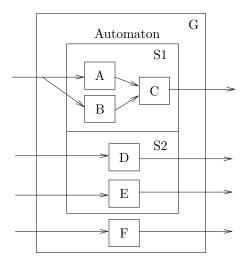

|   |       | 6.3.2.2 Special Case for Automata                                                                              |

|   | 6.4   | Conclusion                                                                                                     |

| _ | -     |                                                                                                                |

| 7 |       | ne-Critial Implementation on the Kalray MPPA2                                                                  |

|   | 7.1   | Related Work on Multi-Core Execution Models                                                                    |

|   | 7.2   | Static Schedule Implementation                                                                                 |

|   |       | 7.2.1 Static Schedule                                                                                          |

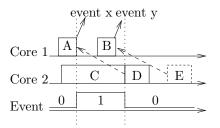

|   | - 0   | 7.2.2 Quasi-Static Schedule: Special Case of Automata                                                          |

|   | 7.3   | System Configuration and Backend Library                                                                       |

|   |       | 7.3.1 Boot Sequence                                                                                            |

|   |       | 7.3.2 Time and Event Synchronization                                                                           |

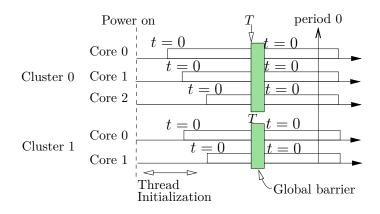

|   |       | 7.3.2.1 Inter-core Synchronization Mechanism on the MPPA2 8                                                    |

|   |       | 7.3.2.2 Time Synchronization Protocol                                                                          |

|   |       | 7.3.3 NoC Configuration and Usage                                                                              |

|   |       | 7.3.4 Cache Maintenance Functions                                                                              |

|   | 7.4   | Communication for a Distributed and Multi-Banked Memory 9                                                      |

|   |       | 7.4.1 Implementation of the Communications                                                                     |

|   |       | 7.4.2 Delayed Communications                                                                                   |

|   | 7.5   | Contribution to Route Allocation                                                                               |

|   |       | 7.5.1 Route Selection and Flow Optimization                                                                    |

|   |       | 7.5.1.1 Exploration for Unique Route Selection (EURS)                                                          |

|   |       | 7.5.1.2 LP-Based Heuristics for Unique Route Selection (LPURS) 9                                               |

|   |       | 7.5.2 Contribution to Multicast Path-Based Routing                                                             |

|   |       | 7.5.3 Deadlock-Free Routing Algorithm for the Kalray MPPA2                                                     |

|   | 7.6   | Deterministic Network Calculus (DNC) Tool                                                                      |

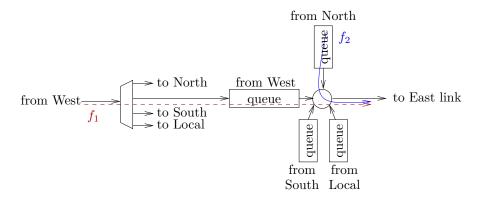

|   |       | 7.6.1 Effects of Link Shaping                                                                                  |

|   |       | 7.6.2 Routers and Network Properties                                                                           |

|   |       | 7.6.3 Arbiter Service Curve 9                                                                                  |

|   |       | 7.6.4 Queue Service Curve                                                                                      |

|   |       | 7.6.5 WCTT Bound                                                                                               |

|   |       | 7.6.6 NoC Configuration Toolchain for the Kalray MPPA2                                                         |

|   | 7.7   | Conclusion                                                                                                     |

|   | • • • |                                                                                                                |

5

# CONTENTS

| Exp | periments 103                                                                                         |

|-----|-------------------------------------------------------------------------------------------------------|

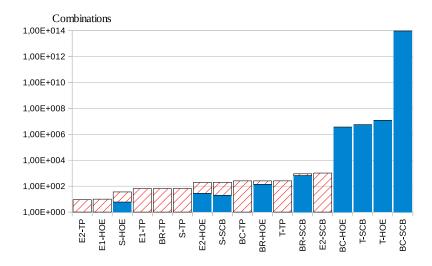

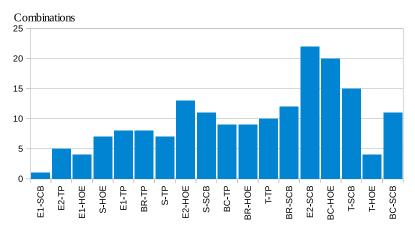

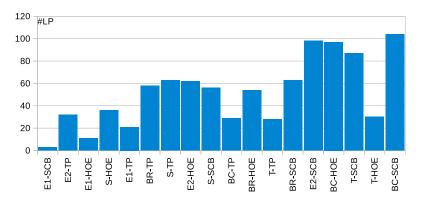

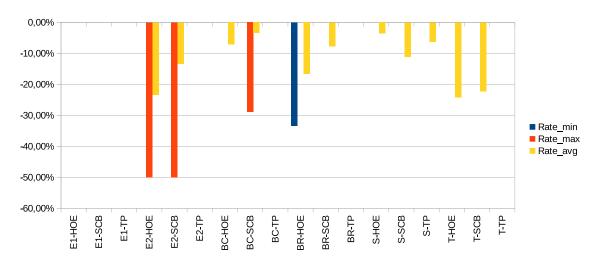

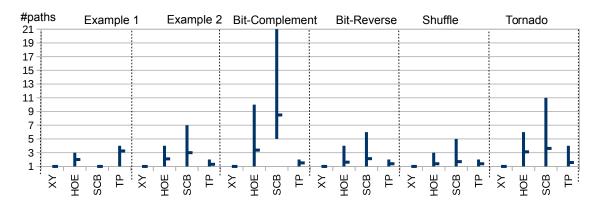

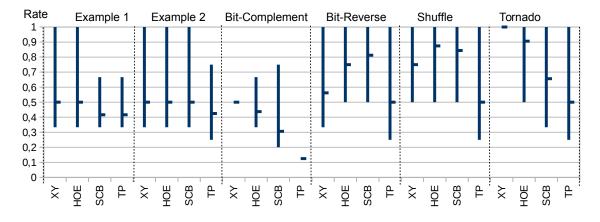

| 8.1 | Route Selection and Routing Algorithm Comparison                                                      |

|     | 8.1.1 Comparison of Deadlock-Free Unicast Routing Algorithms                                          |

|     | 8.1.2 Evaluation of the HOE-DP Unicast-Based Multicast Routing Algorithm 106                          |

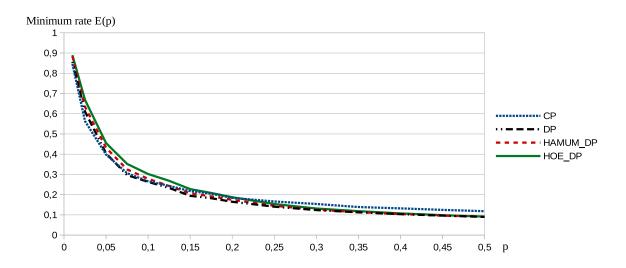

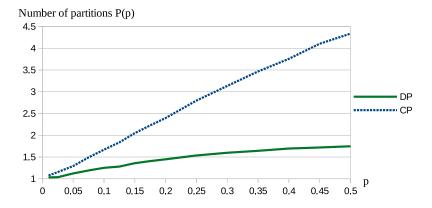

| 8.2 | Comparison of the DNC Formulations                                                                    |

| 8.3 | Case Studies                                                                                          |

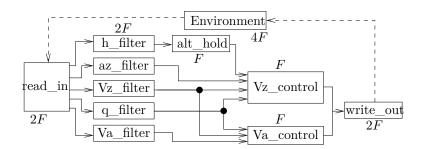

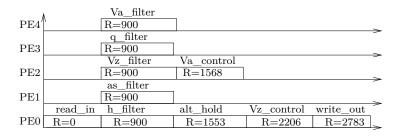

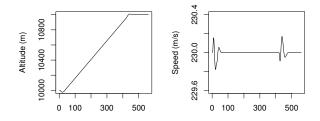

|     | 8.3.1 ROSACE: Flight-Control Use-case                                                                 |

|     | 8.3.2 Sensors Processing Case Study                                                                   |

|     | 8.3.3 Synthetic Benchmark                                                                             |

| 8.4 | Conclusion                                                                                            |

| Cor | nclusion and Future Work 119                                                                          |

| 9.1 | Summary and Contributions                                                                             |

|     | 9.1.1 Task Extraction and Parallel Intermediate Representation (PIR) 119                              |

|     | 9.1.2 Latency-Bounded Communication Under Interference                                                |

|     | 9.1.3 Results                                                                                         |

| 9.2 | Future Work                                                                                           |

| 9.3 | Future of the Multi-Core for Critical Applications                                                    |

|     | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>Con</li> <li>9.1</li> <li>9.2</li> </ul> |

$\mathbf{6}$

# Remerciements

Je voudrais remercier les personnes qui ont été à mes côtés durant ces 3 ans.

En premier lieu, je remercie mes directeurs de thèse, Matthieu et Pascal du laboratoire Verimag qui m'ont beaucoup appris et guidé ainsi que Claire pour ses conseils et son enthousiasme. Je remercie aussi vivement Benoît qui m'a proposé cette thèse chez Kalray et m'a transmis ses connaissances à la fois théoriques et industrielles. Je remercie le jury et les rapporteurs pour avoir relu ce manuscrit.

En second lieu, je remercie les collègues de Kalray, notamment Vincent et l'équipe hardware pour leur connaissance du processeur au cycle près. Merci à la BU Automotive, et aux thésards de Kalray anciens et nouveaux, Julien, grand druide du débug et de l'optimisation, et Cyril.

Je voudrais remercier les autres thésards/docteurs de l'écosystème CAPACITES avec qui il a été agréable de travailler: Hamza et Moustapha (que je n'oublie pas de citer cette fois). Merci aux amis du labo, de la coinche et du Kubb: Denis, Anaïs, Maxime et Thomas.

Enfin, je remercie tous ceux avec qui j'ai passé les soirs et les weekends. Merci à ma famille qui m'a soutenu: notamment mes parents, mon frère, mes grands-parents et Manon. Merci aux amis: Stéphane pour nos discussions jusqu'à tard le soir, Lou pour risquer fréquemment sa vie pour nous offrir du gâteau au caramel, et les pharmaciens.

Merci à l'association Théâtre à Grenoble INP pour le concentré de bonne humeur qu'elle a su générer et Florian de DAF. Merci à ceux que j'oublie.

Je n'oublie pas Skippy, Charade, Larzac, Béa, Billy, les mouchillons et les oiseaux de l'ORTF.

CONTENTS

# Résumé

# 1.1 Introduction

# 1.1.1 Applications temps-réel dur

Des millions de lignes de code [32] font tourner les objets que nous utilisons dans la vie de tous les jours. Ces logiciels améliorent le confort et la sûreté des avions, facilitent la conduite des voitures, réduisent la consommation énergétique ou augmentent la productivité des centrales énergétiques. Ces logiciels influencent directement notre sécurité, à la fois parce qu'ils améliorent la sécurité des systèmes et parce qu'une erreur dans leur code peut être dramatique.

Les systèmes réactifs [67] réagissent à leurs entrées à une vitesse définie par l'environnement. Par exemple, le système anti-collision d'un voiture freine lorsque la distance à l'obstacle est trop courte. En aéronautique, le système de commande de vol réagit en permanence à son environnement et en fonction des commandes du pilote. Ainsi, une réponse trop tardive à une commande ou à un changement de l'environnement est une erreur critique. On appelle temps-réel critique ou temps-réel dur un logiciel qui doit garantir des bornes sur son temps de réaction. Ces contraintes de temps sont spécifiées sous forme de latences, de délais ou de bandes passantes.

# 1.1.2 L'impact des évolutions matérielles sur les logiciels temps-réel

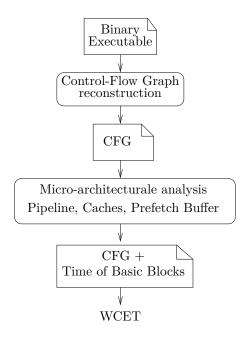

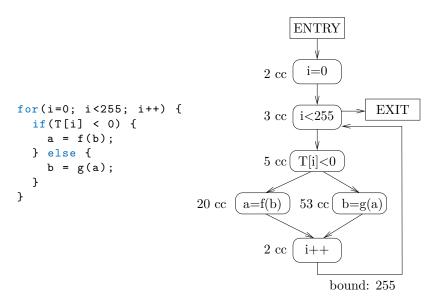

**Mono-cœur.** De nombreuses recherches on été menées dans le but de calculer une borne supérieure des temps de calcul sur des processeurs mono-cœurs. L'analyse de pire temps d'exécution (*worst-case execution time*, WCET) [8, 126] en est un exemple. La durée d'exécution d'un programme dépend du matériel et donc l'analyse requiert un modèle fidèle de celui-ci.

En général, l'analyse de WCET n'est pas exacte : pour être fiable, elle doit sur-estimer la durée réelle d'exécution. La précision du calcul du WCET dépend du matériel. Par exemple des processeurs très simples qui exécutent les instructions dans l'ordre et qui n'ont pas de prédiction de branchement autorisent un analyse très fine. Les comportements dynamiques sont moins prédictibles. Un cache mémoire est aussi un source de non déterminisme si sa politique d'éviction est non prédictible. En conclusion, l'analyse temporelle est plus facile sur du matériel qui autorise la composition des temps d'exécution (*time-compositional* [127] hardware).

La précision de l'analyse du matériel peut parfois être contrôlée par le logiciel : certains processeurs proposent des instructions pour limiter l'indéterminisme ; par exemple en désactivant les caches mémoires. Les modèles d'exécution spécifient la manière dont les programmes doivent être exécutés. Certains modèles d'exécution restreignent l'utilisation du processeur en désactivant tous les mécanismes qui ne sont pas prédictibles.

**Des mono-cœurs aux multi-cœurs.** Aujourd'hui, nous observons deux tendances : la production des mono-cœurs diminue et les logiciels embarqués sont de plus en plus complexes et requièrent de plus en plus de puissance de calcul [114].

Par conséquent, le multi-cœur est à la fois un besoin et une solution. Le multi-cœur sur puce (MPSoC) est une solution pour intégrer plus de fonctionnalités dans le même circuit réduisant ainsi le poids et la consommation des systèmes. Les pluri-cœurs (*many-core*) sur puce ont été inventés pour permettre l'intégration de plus de systèmes sur la même puce. Ils sont composés de dizaines, voire de centaines de cœurs. Il disposent d'un réseau sur puce (NoC) pour minimiser les coûts de communication.

L'isolation temporelle permet d'intégrer plusieurs applications dans le même processeur mono-cœur. Les applications sont isolées car elles ne s'exécutent pas en même temps. De plus, si l'état des registres est parfaitement sauvegardé et restauré lors du changement de contexte, alors l'isolation est parfaite et le WCET de chaque partie peut être calculé séparément.

Pour les multi- et les pluri-cœurs, l'isolation peut être basée sur le temps, l'espace ou les deux. L'isolation spatiale consiste à exécuter des processus sur des cœurs différents, utilisant des espaces mémoires différents. Néanmoins, un compromis doit être trouvé entre l'isolation et la communication. En d'autres termes, l'isolation n'est pas parfaite et les différents cœurs ont besoin de communiquer en utilisant des ressources partagées. Ainsi, le comportement d'un processus a un impact sur les autres.

Par exemple, l'accès mémoire d'un cœur peut être retardé par l'accès concurrent d'un autre cœur à la même ressource. Ces accès concurrents sont des interférences et ne sont pas limités à la mémoire : les bus, les réseaux sur puce (NoC), les ports d'entrées/sorties, les caches partagés soufrent aussi des interférences.

La cohérence de cache est un mécanisme assurant que, pour une adresse mémoire donnée, la donnée est la même dans le cache de tous les cœurs. Par exemple, un accès mémoire peut être provoqué même s'il n'y a pas de défaut de cache si la valeur présente dans le cache n'est pas à jour. Le principal inconvénient est que du point de vue d'un cœur, le temps d'accès n'est pas prévisible puisqu'il dépend des accès des autres cœurs à la même ligne de cache. Lorsque la cohérence de cache est implémentée par logiciel, la mise à jour du contenu du cache est explicite ce qui rend l'analyse temporelle plus facile.

Les multi-cœurs dans l'industrie critique. Dans l'industrie aéronautique, le CAST-32A est un document qui explique le point de vue des autorités de certification sur l'usage des multi-cœurs [48].

L'utilisation de multi-cœurs pour les systèmes aéronautiques requiert l'énumération exhaustive et la compréhension complète des sources d'interférences. Le CAST-32A décrit le partitionnement robuste comme une propriété du système où chaque cœur utilise uniquement les ressources qui lui ont été assignées. L'utilisation des ressources par un cœur doit se faire dans le respect des contraintes temporelles des autres cœurs. Les erreurs à l'exécution qui sont spécifiques aux fonctionnalités du multi-cœur doivent être détectées et prises en compte.

# 1.1.3 L'usage des multi- et pluri-cœurs pour des applications critiques

La recherche sur l'analyse du WCET sur multi-cœur est très active. Des travaux traitent de l'analyse d'interférences [43, 113, 120, 81], de la programmation de ces multi-cœurs pour minimiser les interférences [105, 82, 104, 10, 47] ou l'ordonnancement des tâches prenant en compte ces interférences. Des travaux proposent des modèles d'exécution isolant totalement les processus en supprimant les interférences [103, 96, 47]. D'autres, comme notre travail, minimisent les interférences et rendent leur analyse possible [113, 119]. Dans notre travail, nous cherchons un compromis entre les performances et l'isolation lors de l'analyse et de la configuration du matériel.

Développer des applications temps-réel dur sur les multi-cœurs pour tirer parti du parallélisme d'exécution tout en minimisant les interférences est un problème d'optimisation multi-critère. Cela nécessite de créer des tâches parallèles et de les déployer sur les cœurs et dans la mémoire. La configuration fine du processeur est aussi nécessaire pour minimiser l'impact des comportements dynamiques du matériel. Par exemple, certains processeurs disposent de cohérence de cache logicielle ce qui rend le processeur plus prédictible mais sa programmation plus complexe.

## 1.2. MÉTHODE GÉNÉRALE

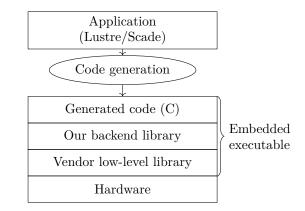

En conclusion, l'utilisation des multi-cœurs pour les applications temps-réel nécessite des logiciels complexes. Cette complexité rend les erreurs de programmation courantes. Une solution est la génération de code depuis un langage haut niveau afin de faciliter l'analyse temporelle [27, 26, 82, 74]. Notre travail en fait parti.

# 1.1.4 La programmation par modèle et les langages synchrones

Les langages synchrones ont été conçus pour faciliter le développement des systèmes réactifs critiques. Ils fournissent une notion de temps abstrait qui facilite la vérification des contraintes de temps. Lustre [68] est un langage synchrone flot de données et Scade [15] est sa version industrielle utilisée par l'industrie avionique.

Les langages synchrones sont des langages haut niveau qui abstraient l'implémentation système. Certains langages synchrones disposent d'une syntaxe graphique facilitant le développement des applications complexes. Il existes des langages similaires non-synchrones tels que Simulink qui permettent de décrire la fonctionnalité de l'application tout en cachant au développeur les problèmes liés à l'implémentation système.

Le développement par modèle sur multi- et pluri-cœurs est basé sur la génération automatique de code depuis la spécification de haut niveau. Les tâches parallèles doivent aussi être extraites automatiquement tout en assurant les critères de performance et de conservation de la sémantique.

# 1.1.5 Résumé des contributions : les programmes synchrones temps-réel dur sur pluri-cœur

Dans cette thèse, nous proposons une méthode complète de génération automatique de code temps-réel critique depuis les langages synchrones Scade ou Lustre vers une cible multi-/pluri-cœur.

Nous appliquons cette méthode au pluri-cœur MPPA2 de Kalray. Néanmoins, notre but est de tirer un enseignement plus large de ce travail pour permettre d'appliquer la méthode à toute une classe de multi-cœurs.

Premièrement, nous définissons une méthode pour extraire des tâches parallèles depuis un programme synchrone. Deuxièmement, nous générons une configuration automatique de la machine pour la rendre prédictible temporellement. La mémoire et le réseau sur puce (NoC) sont configurés afin de maîtriser les interférences. En particulier, nous implémentons un outil de configuration du NoC qui permet des communications sans interbloquage et le calcul de la latence de bout en bout.

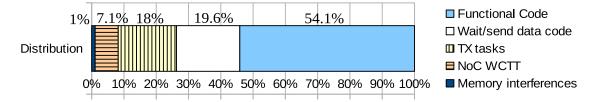

Enfin, notre outil génère le code système nécessaire à l'implémentation des tâches de communication, la synchronisation et l'isolation spatiale. Un binaire est généré par assemblage du code fonctionnel, du code système et de la configuration du processeur.

La méthode de génération de code et les expériences on été publiées dans [63] et la méthode générale a été soumise pour publication dans [64]. La méthode de routage sur le NoC, sa configuration et les méthodes de calcul de latence on été publiées dans [21, 46, 45].

Nous présentons maintenant la méthode générale.

# 1.2 Méthode générale

Nous expliquons la méthode globale pour l'implémentation parallèle d'un programme synchrone flot de données sur processeurs pluri-cœurs.

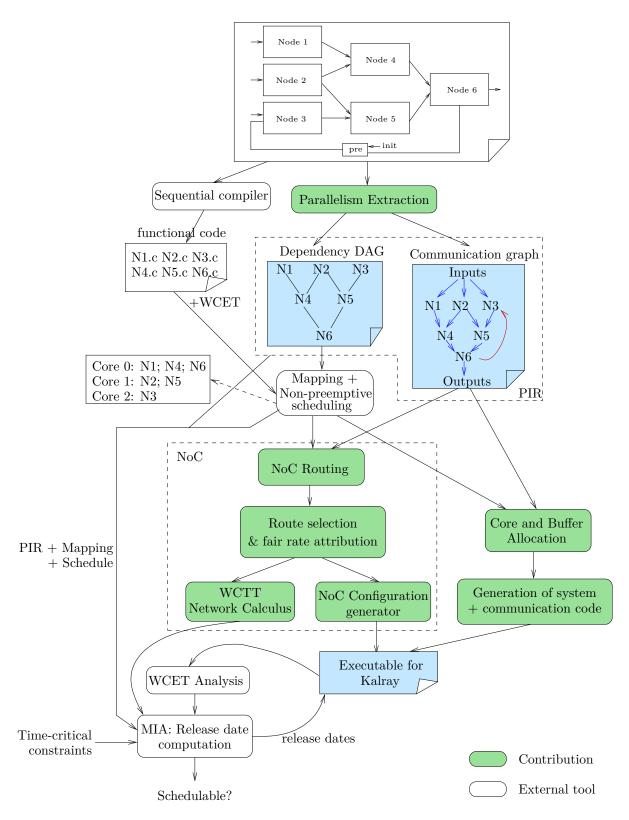

La *Représentation Intermédiaire Parallèle* (PIR) décrit le programme comme un ensemble d'entités communiquant entre elles. Le PIR sépare le problème en deux : l'extraction du parallélisme depuis le programme d'entrée et l'implémentation du PIR sur un pluri-cœur.

# 1.2.1 Définition de la Représentation Intermédiaire Parallèle

Le PIR doit être assez précis pour rendre l'implémentation du programme possible mais suffisamment abstrait pour permettre le raisonnement.

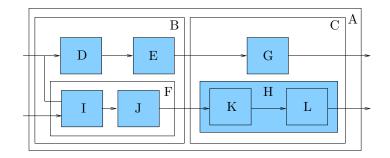

Le PIR naturel d'un programme flot de données est basé sur la division en nœuds. Il ne décrit pas la fonctionnalité du programme mais contient un ensemble de nœuds communiquant ensemble.

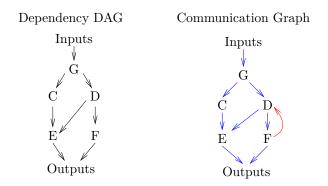

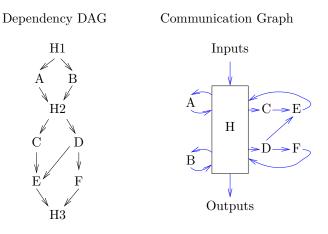

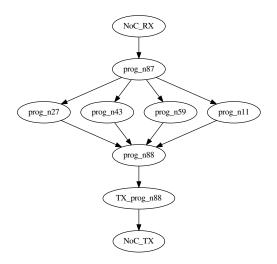

Le PIR est composé d'un graphe acyclique décrivant les dépendances entre les tâches. Les langages synchrones permettent les communications directes ou les communications avec délais (opérateur pre). Seules les dépendances directes sont décrites par ce graphe. Le graphe est acyclique et décrit un ordre partiel entre les nœuds sous la forme de contraintes de précédence.

Le graphe de dépendances décrit les canaux de communications entre les nœuds. Il peut être cyclique si l'une des communications formant le cycle a un délai. Chaque canal décrit la taille de la communication ainsi que le nombre de délais.

Le graphe de dépendances est utilisé pour ordonnancer les tâches et générer les synchronisations tandis que le graphe des communications est nécessaire pour implémenter les canaux de communications.

## 1.2.2 Extraction des tâches parallèles

Le but de l'étape [Extraction du parallélisme] est d'extraire les tâches depuis le programme afin de générer le PIR. Notre méthode extrait les tâches depuis le nœud de plus haut niveau dans la hiérarchie du programme. Un tâche est créée pour chaque sous-nœud. Ces tâches sont candidates pour être exécutées en parallèle. Les tâches, les dépendances et les communications sont obtenues par analyse syntaxique du programme.

Cette méthode est similaire à celle employée par les langages de description d'architecture (ADL) tels que Prélude ou Giotto.

Le code fonctionnel de l'application est obtenu en compilant chaque nœud avec un compilateur Lustre ou Scade standard.

### 1.2.3 Choix d'implémentations pour tirer parti des bancs mémoire

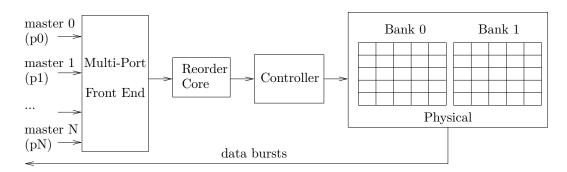

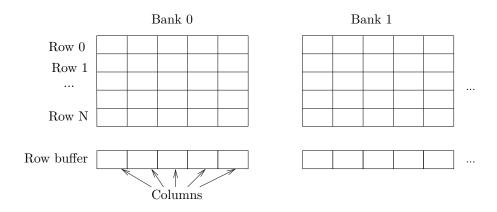

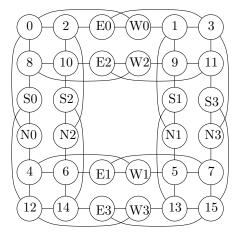

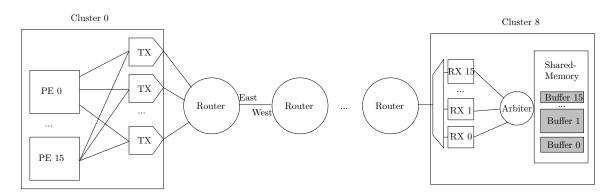

Kalray MPPA2. Le MPPA2 de Kalray est un pluri-cœur composé de 16 clusters. Chaque clusters s'apparente à un multi-cœur de 16 cœurs et d'une mémoire partagée. Cette mémoire partagée est composée de 16 mémoires indépendantes appelées bancs. Les clusters sont reliés entre eux par un réseau sur puce (NoC) composé de liens et de routeurs. Chaque cluster est un nœud de ce réseau et peut écrire dans la mémoire d'un autre cluster. Chaque communication NoC peut se faire à travers un limiteur de bande passante matériel.

Dans cette section, nous présentons les problèmes et les choix techniques liés à la mémoire partagée.

**Communication : lecture distante ou écriture distante.** Nous considérons des plateformes avec une mémoire distribuée ou une mémoire composée de plusieurs bancs.

Un banc est associé à chaque cœur. Nous parlons d'écriture distante lorsqu'une donnée est copiée par un cœur vers la mémoire d'un autre cœur. À l'inverse, nous parlons de *lecture distante* lorsqu'une donnée est lue par un cœur dans une mémoire distante.

Dans notre travail, nous choisissons l'écriture distance puisqu'elle permet d'être cohérent avec le fonctionnement du NoC du MPPA2 qui donne un accès direct en écriture aux mémoires distantes.

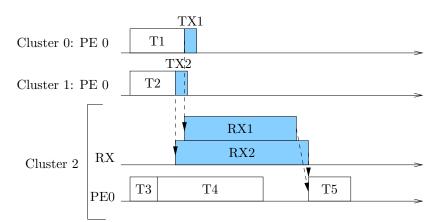

Modèle d'exécution dirigé par le temps. Les nœuds des programmes flot de données sont exécutés lorsque leurs entrées sont disponibles. Pour reproduire le fonctionnement flot de données sur un multi-cœur, on peut utiliser des synchronisations. Dans ce cas, les tâches sont exécutées sur l'occurrence d'un évènement. Une autre manière est de programmer le démarrage de chaque tâche sur des dates fixées pour lesquelles on est certain que les entrées sont disponibles. Dans ce cas on parle d'exécution dirigée par le temps.

## 1.2. MÉTHODE GÉNÉRALE

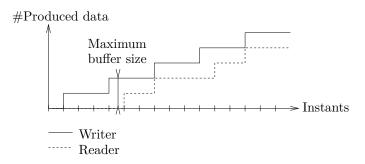

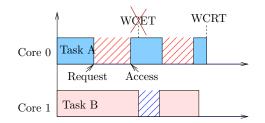

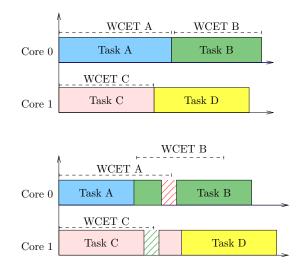

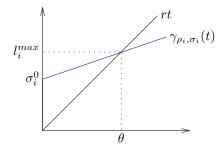

Nous analysons les interférences pour chaque tâche. Deux tâches peuvent interférer lorsqu'elles utilisent simultanément le même banc mémoire. Le pire temps d'exécution d'une tâche (WCET) est calculé sans prendre en compte les interférences. Ainsi, la durée d'exécution réelle peut être supérieure au WCET s'il y a des interférences. Pour cela on calcule le pire temps de réaction (WCRT) qui prend en compte les interférences.

Si les tâches d'un programme démarrent dès que possible, il est difficile de calculer un WCRT précis puisqu'un changement dans la durée d'exécution d'une tâche peut rendre concurrentes des tâches qui ne l'étaient pas. Pire, un temps d'exécution plus court pour une tâche peut mener à un temps d'exécution globalement plus long.

Ainsi, nous choisissons une exécution dirigée par le temps pour laquelle chaque tâche dispose d'une date de démarrage définie statiquement. Les tâches ne peuvent pas démarrer plus tôt que leur date de démarrage. Cela permet d'éviter les problèmes dus à la durée d'exécution des tâches.

Rihani *et al.* [113] introduisent un modèle d'exécution dirigé par le temps et un outil capable de calculer les dates de démarrage de chaque tâche en prenant en compte les interférences et les dépendances. Nous utilisons cet outil pour permettre l'exécution dirigée par le temps.

# 1.2.4 Implémentation du PIR sur un pluri-cœur

Une fois le PIR extrait, il peut être implémenté sur la plateforme. Son implémentation doit conserver la sémantique du programme d'entrée et satisfaire les contraintes de temps. La génération de code est découpée en différentes étapes que nous décrivons maintenant.

**Déploiement et ordonnancement statique.** L'étape [Mapping+Scheduling] (placement et ordonnancement) est basée sur un outil externe pour trouver un placement optimisé des tâches sur les cœurs et les clusters du processeur. Puis, l'outil calcule un ordonnancement compatible avec le graphe de dépendances.

Il peut choisir d'optimiser la durée du chemin critique du programme. Cela nécessite de connaitre la durée d'exécution de chaque tâche. Néanmoins, ces temps d'exécutions dépendent des interférences qui dépendent à leur tour du placement.

Cette interdépendance entre le placement et la durée d'exécution peut être vu comme un problème avec un point fixe. Nous choisissons de casser la boucle en utilisant le WCET comme durée d'exécution de chaque tâche. Par conséquent, l'outil de placement et d'ordonnancement requiert le graphe de dépendances et le WCET en isolation de chaque tâche.

L'ordonnancement est statique et non préemptif. Cela évite les problèmes dus à la préemption et simplifie le calcul du WCRT.

Un banc mémoire est associé à chaque cœur. Le code, les données et les tampons de communication sont placés sur le banc correspondant au cœur. Par conséquent, chaque cœur accède exclusivement à son propre banc, sauf quand il communique. Ce principe est réalisé par l'étape [Code and Buffer Allocation].

**Date de démarrage des tâches et exécutable final.** L'étape [WCET Analysis] a pour but de calculer le WCET de chaque tâche en isolation. Les outils d'analyse de WCET OTAWA [8] et AiT [50] sont compatibles avec le MPPA2.

L'étape [MIA: Release date computation] correspond à l'outil MIA [113] qui calcule les dates de démarrage des tâches en prenant en compte la précédence et les interférences.

L'étape [Generation of system + communication code] (génération du code système et du code de communication) génère le code pour démarrer les cœurs, le code pour implémenter l'ordonnancement statique et les communications. Pour l'implémentation dirigée par le temps, cette étape nécessite les dates de démarrage des tâches. Cependant, puisque la compilation du binaire a un impact sur la durée d'exécution du programme, le WCET des tâches est calculé sur le binaire final. Mais ce binaire final nécessite les dates de démarrage des tâches.

Ainsi, nous avons choisi d'intégrer les dates de démarrage en modifiant le binaire final.

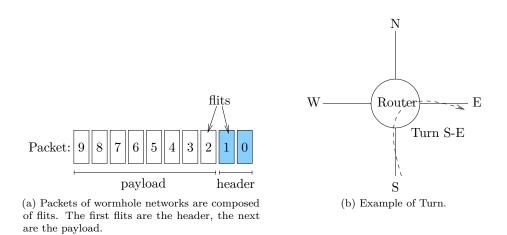

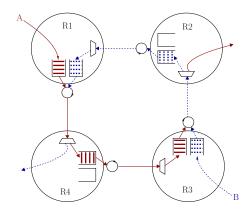

Routage et pire temps de traversée NoC. Lorsque des tâches de différents clusters communiquent, le canal de communication passe par le NoC. Cette communication à travers le NoC est appelée *flux*.

Nous choisissons de configurer le NoC avec des routes statiques et un limiteur de bande passante pour chaque flux. Par conséquent, la configuration du NoC nécessite deux paramètres pour chaque flux : la route et la bande passante. Cette configuration facilite le calcul du pire temps de traversée du NoC appelé *WCTT*.

Le WCTT est nécessaire pour l'étape [MIA: Release date computation].

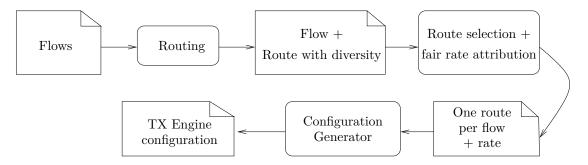

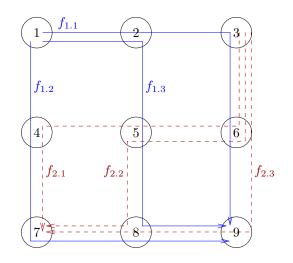

L'étape [NoC Routing] calcule l'ensemble des routes possibles pour chaque flux. Pour cela, il est nécessaire d'utiliser des algorithmes de routage garantissant l'absence d'interbloquage. Nous comparons différents algorithmes de routage point à point sur le MPPA2 et nous présentons un algorithme de routage 1-N (multicast) qui minimise le nombre de ressources NoC nécessaires à son implémentation.

L'étape [Route selection & fair rate attribution] sélectionne une seule route par flux. Pour que la bande passante de chaque lien du réseau soit distribuée équitablement entre les flux, nous utilisons le critère de *max-min fairness* [33]. Lorsque les bandes passantes des flux respectent ce critère, l'augmentation de la bande passante d'un flux ne peut pas se faire sans réduire la bande passante d'un flux déjà inférieur. Nous présentons un algorithme fournissant une solution optimale et une heuristique basée sur de la programmation linéaire pour implémenter ce critère.

L'étape [NoC Configuration generator] génère l'entête des paquets contenant la route sélectionnée. Il génère aussi la configuration du limiteur de bande passante.

L'étape [WCTT Network Calculus] utilise la théorie du Network Calculs pour calculer le WCTT de chaque flux.

# 1.3 Conclusion

Nous proposons un ensemble d'outils permettant la génération de code depuis un programme synchrone flot de données vers un processeur multi- ou pluri-cœur. Ces travaux ciblent des applications critiques et temps-réel dur qui nécessitent la correction du fonctionnement. En particulier, le code généré doit permettre la validation du logiciel et la traçabilité du code. L'objectif final est de garantir des contraintes de temps exprimées sous forme de bandes passantes minimales ou de latences. L'implémentation est réalisée sur le Kalray MPPA2. Les résultats des expériences sont prometteurs puisqu'ils montrent une accélération importante due à la parallélisation tout en offrant des garanties sur le temps d'exécution.

# 2

# Introduction

# 2.1 Hard-Real-Time Applications

Millions of lines of code [32] are involved in our everyday life to improve comfort in planes, ease the driving of cars, lessen energy consumption and raise the energy production of plants. Most of these lines of code are critical and directly related to user safety: either because their purpose is to improve safety, or because an unexpected software behavior can endanger people.

Reactive systems [67] react to external events or values at a speed defined by the environment. For instance, the collision avoidance system in cars triggers an emergency brake if the obstacle distance is too short. In avionics, control systems are constantly reacting to changes in the environment to maintain the pilot command. A too late response to events or environment changes leads to unexpected behavior. Furthermore, we name time-critical or hard real-time, softwares that must guarantee bounds for the computation time. Timing constraints such as latency, delays or bandwidth of the systems are part of the specification of the system.

# 2.2 Impact of Hardware Evolution on Time-Critical Software

# 2.2.1 Single-Core

Extensive research has been carried out to formally assess bounds on the computation time of a program on single-core processors. The worst-case execution time (WCET) analysis [8, 126] is a general solution to compute an upper bound on the execution time of a program under the worst conditions. Indeed this duration depends on the hardware. Therefore an accurate model of the hardware behavior is required.

In general, the WCET analysis cannot be exact, therefore to be sound it must be overestimated. Some cores provide a tighter overestimation than others. This is the case of processors with simple pipeline compared to processors with an out-of-order pipeline or branch prediction. Dynamic behavior makes predictability harder. A cache is also a source of indeterminism if its eviction policy is not predictable. Finally, time-compositional [127] hardware makes the timing analysis easier.

The software has an impact also on the accuracy of the analysis. An execution model specifies the way programs are executed. Some execution models define a restricted usage of the processor ensuring time-predictability by disabling some unpredictable processor behaviors.

# 2.2.2 Single-Core vs. Multi-/Many-Core

Today, we observe a twofold trend. Single-core processors are less and less produced and the software is more and more complex in embedded systems leading to an increasing demand for computing power [114].

Consequently, multi-core is seen both as a solution and a necessity. Multi-core system-on-chip (SoC) can be used either as a way to increase computing power, or a way to integrate more functionality

in the same piece of hardware; thus reducing weight, space and power consumption of systems. The many-core system-on-chips (SoC) has been invented in anticipation of this integration of several systems and functions in the same processors. Many-cores embed tens to hundreds of cores in the same SoC and provide optimized bus or network-on-chip (NoC) to minimize communication cost.

Integrating several functions in the same single-core processor is done using time isolation, meaning that the different isolated processes are not executed at the same time. Furthermore, if the state of the hardware is exactly saved and restored at each process switch, this isolation is perfect and the computation of the WCET of each piece of software can be done separately.

For multi- and many-core processors their isolation can be based on time, on space or both. The spatial isolation consists in executing different processes on different cores or making them use different memory spaces. Nevertheless, multi- and many-core processors offer a trade-off between the ability of the process to communicate and their isolation. In other words, since the spatial isolation is not perfect and since the inter-process communication is required, processes have an impact on each other.

Resource sharing has an impact on the processes execution time. For instance, memory access of one core can be delayed due to a concurrent access of another core. Such concurrent access is called interference. The interference is not limited to memory: bus, network-on-chip, input/output ports, shared caches, and other shared resources suffer from interference.

Coherent caches ensure that for the same address, the value is the same in the memory and in the caches of the other cores. For instance, a cache hit can lead to a memory access if the value is not up to date. The main drawback is that from the point of view of one core, the access time is unpredictable since it depends on the access of the other cores to the same cache line. For software-based coherent caches, an update of cache contents is explicitly triggered by software thus making the access time more predictable.

In the avionics industry, the CAST-32A document explains the position of certification authorities about multi-cores [48]. Using multi-cores for avionic systems requires understanding completely the sources of interference. The document gives a definition of robust partitioning where a core use only the resources assigned to him and the resource usage of the other cores has no impact on the deadline of this core. The runtime errors specific to the multi-cores features must be detected and handled.

# 2.2.3 Multi-/Many-Core for Time-Critical Applications

There is an active research on the analysis of WCET for multi-core including the interferences [43, 113, 120, 81], on programming multi-core in a way that minimizes interferences [105, 82, 104, 10, 47] or on tasks scheduling taking into account the interferences. Some work design execution models whose purpose is to isolate processes. Some execution models totally isolate processes by preventing interferences [103, 96, 47]. Others minimize interferences and make the impact of concurrency of execution time analyzable [113, 119]. Our work belongs to this category where a fine analysis and configurations of the hardware are performed to trade between performance and isolation.

Developing time-critical applications on multi-/many-cores that take advantage of the execution parallelism while minimizing interferences requires to solve a multi-criteria optimization problem. This requires creating parallel tasks and mapping them on the core and the memory. This also requires a fine configuration of the processor to minimize the impact of non-predictable mechanisms. For instance, some processors offer software-based cache coherency that is more predictable at the cost of more complex and error-prone software.

We can conclude that using a multi-core for time-critical applications leads to complex software and can be error-prone. One potential solution is the code generation from a high-level program. There is an active research in time-predictable software code generation for multi-core [27, 26, 82, 74] which enables timing analysis methods. Our work belongs to this category.

# 2.3 Model-Based Development and Synchronous Languages

Synchronous languages have been invented to ease the development of critical reactive systems. They provide an abstract notion of time designed to ease the verification of the timing constraints. Lustre [68] is a data-flow Synchronous language and Scade [15] the industrial version of Lustre used by the avionics industry.

Synchronous languages are high level languages that abstract the implementation from the developer view. Some Synchronous languages are provided with a graphical syntax easing the development of complex applications. There are similar languages such as Simulink which enable to describe the functionality of the application while abstracting the processor and system problems.

The requirements of model-based development is twofold. First, it requires code generation for complex processor from the functional code. Second, it needs an automatic parallelism extraction which ensures both performances and semantics preservation.

# 2.4 Contributions Overview: Time-Critical Synchronous Program on a Many-core

In this thesis, we propose a complete method to automatically generate time-critical parallel code from Lustre and Scade to a multi-/many-core processor. We apply our method on the Kalray MPPA2 many-core architecture, nevertheless, the purpose of our work is to learn a wider lesson that could be applied other multi-core processors.

First, we define a method to extract parallel tasks from the Synchronous program. Second, our work performs an automatic configuration of the machine in a mode enabling time-predictability. The memory and the network-on-chip are configured to minimize interferences. In particular, we implement a network-on-chip configuration tool to enable end-to-end latency computation and deadlock-free communication.

Then, our tool generates the system code used to implement task communications, synchronizations and spatial isolation. Finally, a binary is generated by assembling the functional code, the system code and the processor configuration.

# 2.5 Organization of This Document

The first chapters of the thesis provide the basis required to understand our approach. Chapter 3 describes the principles and motivations for the model-based design from data-flow Synchronous languages and we compare them to other parallel languages for reactive systems. Chapter 4 presents the main timing problems of multi-core and presents existing methods to cope with them. We present some existing architectures and in particular the Kalray MPPA2.

The general method of our work is exposed in Chapter 5. This chapter can be used as a table of contents pointing to the bricks composing this work. The method and some experiments have been published in [63] and the overall flow has been submitted for publication [64].

The next chapters present the implementation of the general method in more details. Chapter 6 explains with a high-level view different methods to extract parallel tasks from a data-flow Synchronous program and defines an intermediate representation format used along the toolchain. In Chapter 7, we discuss the complete implementation of our toolchain and the execution model for the MPPA2. This chapter also exposes the NoC routing and configuration and delay computation which have been published in [21, 46, 45].

Finally, in Chapter 8, we apply our method to some avionics use cases. In Chapter 9, we discuss the results and suggest future improvement to our work.

# **3** Background: Synchronous Programs & Parallelization

# 3.1 Reactive Systems and Synchronous Languages

In this section, we present the context and usage of the Synchronous languages. Automatic controllers are used in industry to control some values of a system by adjusting the value of some actuators. These systems are widespread in plants and transportation. Examples can be found in avionics with the altitude or speed control, in automotive to control the idle speed of the motor by controlling accelerator, in energy (see Example 1 for a wind turbine), etc. These systems have reaction latency constraints.

**Example 1.** Recent wind turbines are controlling the speed of the rotor to maximize the energy production. Rotor speed is controlled by acting on the blades angle. A too fast rotation of the rotor can damage the system; hence the control system has to ensure that the speed remains below the limit. The angle of the blades must be controlled fast enough to keep the rotor speed to the limit, maximize energy production and avoid damage [97].

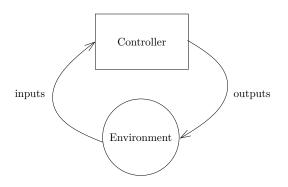

Systems designed to implement control engineering problems have been formalized as Reactive Systems by David Herel and Amir Pnueli [70].

Reactive systems are systems constantly reacting to the environment at a speed defined by this environment [67]. The principle of a such system is shown in Figure 3.1. These systems have to be reliable because they are often safety critical and can possibly execute for years without been stopped. Figure 3.2 shows a reactive program executing in an infinite loop (while(true)). The read function generally consists in sampling on the inputs. The delay between the call to read and the call to write is named reaction time.

In this chapter, we only focus on the compute function. The reason is that reading the inputs and writing the outputs are orthogonal problems which rely on low-level platform-specific programming.

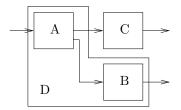

Figure 3.1: Reactive Program Principle

```

while(true) {

inputs = read();

output = compute(&memory, inputs);

write(outputs);

}

```

Figure 3.2: Simple Reactive Program

Each call to the compute function is one reaction. The result of this reaction depends on the current inputs and previous computations stored in memory.

Synchronous languages have been invented to program reactive systems. We now define the main reasons why synchronous languages are well adapted for this purpose.

**Determinism.** A program is deterministic if for the same sequence of inputs, the same sequence of outputs is produced. An equivalent assertion is that for the same internal memory state and the same inputs, the program computes the same output. This is essential to guarantee the testability of the program. When high assurance is required mathematical proof is able to ensure functional correctness of the program. A requirement is that the language, and thus the program, has well-defined semantics. Synchronous languages have well defined semantics and a Synchronous program can be compared to an automaton.

To ease the development of complex systems, synchronous programs are modular and parallel. Synchronous languages are based on the notion of synchronous product of automata where at each transition of the resulting automaton, one transition of each automata is taken. A property is that a synchronous product of deterministic automata is deterministic [88]. On the other hand, the asynchronous product of deterministic automata does not necessarily lead to a deterministic automaton.

**Synchrony Assumption.** Implementing control software with classical languages such as C can be complex since there is no built-in notion of time. The Synchronous languages have been historically designed for this purpose. They provide a formal notion of time abstracting the host machine physical execution time.

Synchronous languages are based on the synchrony assumption where all inputs/outputs events occur on a logical clock. This clock is discrete and global. Each instant is defined on the logical time. As a result, the semantics of the program is independent from physicist time and execution time [67, 13]. The program reacts on this clock and thus does not depend on the system speed. The determinism is then enforced. This logical clock can represent physical time, kilometers or any measurement.

A good property is that the values of a variable are defined on this logical clock. In other words, the value of a variable at a previous instant stays accessible. For instance in automatic control, this allows a clear expression of the differential equations.

**Bounded Memory and Execution Time.** Engineers of a system must check that the reaction of the program (compute in Figure 3.2) between the moment the inputs are read and the moment the outputs are written is fast enough to comply with the physical requirements. In order to guarantee that reaction time is bounded, synchronous languages are voluntary limited to static memory allocation, non recursive function and bounded loop. This can be statically verified on the compiled code with the *Worst-Case Execution Time (WCET)* upper bound. In other words, the Synchronous Assumption guarantees the qualitative real-time. The quantitative real-time must be checked afterward by construction.

In this step, the synchrony assumption is checked, meaning that we verify that the logical instants can be executed on the required clock.

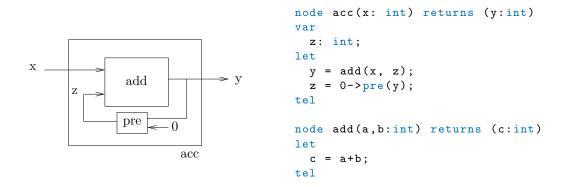

Figure 3.3: Example of accumulator in counter in both textual and graphical Lustre computing the sum of the successive values of x.

**Formal Semantics.** Synchronous languages have formal semantics. The synchronous hypothesis makes the program behavior independent from the machine specificities. If the compiler preserves the semantics of the program, tests and verifications can be done at the program level instead of the generated code. This is the basis of the model-based design.

Model checking is a method that verifies properties on a model. With Synchronous languages, it is done in two steps: the properties that have to be checked and the constraints from the environment are encoded into an observer. An example of properties is *The two doors cannot be open at the same time*. Usually this observer produces a single Boolean indicating if the property is valid. A model checker verifies these properties by considering all the states of the program. Examples of model checker are Lesar [110], Kind2 [31], NP-TOOLS [92] or SCADE Design Verifier<sup>1</sup>. If the properties do not hold, the model checker exhibits trace leading to this problem.

**Programming Style.** Synchronous languages are either data-flow or control-flow (imperative). Lustre and Signal are data-flow whereas Esterel [16] and Statecharts are control flow. Some synchronous languages provide a graphical representation such as Argos [95] or Scade [15]. The data-flow describes relations between the data whereas the control-flow controls the execution of the program. In the graphical representation, data-flow programs are composed of component linked with arrows where one arrow is a data. Control-flow programs are represented with states and transitions between these states. This allows to modularly describe complex automata. For this reason Esterel has been used for circuit design in industry.

Details on Lustre are given in Section 3.1.1. Scade is an industrial language combining both Lustre and Esterel. The Scade automata are explained in Section 3.1.2.2.

#### 3.1.1 The Core Language: Lustre

Lustre is a data-flow synchronous language. It is based on the synchronous hypothesis, as explained in Section 3.1.

A data-flow language. A data-flow program describes well-separated entities that communicate together allowing a clear extraction of the communication information. Entities of Lustre are called nodes and a program is a node which contains a network of sub-nodes. The communication between the nodes are expressed with a set of equations which are composed of node calls, data operations (arithmetic, logic) or timing operations (e.g., atomic delay, called **pre**). Node is the compilation unit

<sup>&</sup>lt;sup>1</sup>http://www.esterel-technologies.com/products/scade-suite/verification-validation/ scade-suite-design-verifier/

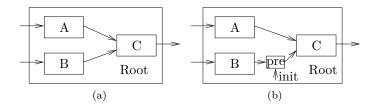

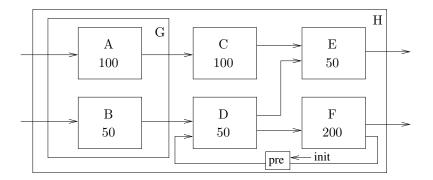

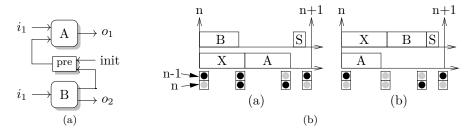

Figure 3.4: Lustre is a dataflow language. Nodes are executed in an order compliant with datadependencies. In (b), the **pre** operator breaks the dependency.

and the modular abstraction. For instance, in Figures 3.3, acc is the top-level node containing a node add and the pre operator.

A synchronous language. Lustre has synchronous semantics: execution is an infinite sequence of atomic reactions. A variable in Lustre is also called flow as its value is function of time. The pre operator allows referencing the value of a flow at the previous logical instant. As the previous value is undefined at the first reaction, we need the arrow operator (->) to specify the initial value as shown in Figure 3.3. A node can depend on its own output and this construction is called feedback loop. In Lustre, a program that depends instantaneously on its outputs (x = f(x)) is illegal. This program would require a fixed-point computation to compile and this fixed-point often does not exist. To avoid this issue, feedback loops are accepted only if a pre operator breaks the loop.

**Example 2.** This table shows timing operations on a flow. At the first instant, pre x is not defined. Hence, the arrow operator is required to initialize the expression. Scade and some variants of Lustre adopt an alternative operator followed-by (fby) that takes both the initial value and the flow as parameter, *i.e.*, 1->pre  $x \Leftrightarrow 1$  fby x.

| Instant  | 1st | 2nd | 3rd | 4th | 5th |

|----------|-----|-----|-----|-----|-----|

| x        | 0   | 2   | 4   | 6   | 8   |

| pre x    | ?   | 0   | 2   | 4   | 6   |

| 1->pre x | 1   | 0   | 2   | 4   | 6   |

Classical Lustre Compilation for Single-Core. In Lustre, a node is expressed as a list of equations defining all outputs and local variables. Each equation is of the form x=e; where e is an expression made of constant, operations, node and external function calls. The compiler sorts the equations according to their dependencies (partial order) to obtain a sequential program. There can be several possible execution order for a program. In Figure 3.4a, the possible sequences are A;B;C or B;A;C. In Figure 3.4b, the dependency between B and C is broken, hence any permutation where A completed before C is possible, *i.e.*, A;C;B, B;A;C or A;B;C.

# 3.1.2 Conditional Computation in Synchronous Data-Flow Languages

Despite their data-flow aspect, the Lustre and Scade offer features to express conditional execution. In this section, we present the Lustre clock and the Scade automata.

#### 3.1.2.1 Clocks in Lustre

Lustre provides a way to specify that parts of a data-flow compute "less often" than other. This is achieved via the notion of clocks.

Clocks in Lustre can be seen as a tree following the same hierarchy as the program. The top-level node is activated at each execution of the program (at each logical instant). Sub-nodes are activated

according to the clock of their inputs. A sub-node of a node is activated at most as often as the node, *e.g.*, it can only be made slower.

In Lustre, a clock is a flow of Booleans. When the Boolean is true the clock is active; when it is false the clock is not. The expression clk = true; defines the always-true clock relatively to the parent node. This clock has the same speed as the parent node: it is active at the same time as the parent node. There are two operators to manipulate the clocks: when and current.

The when operator as in expr when clk creates a flow slower than expr. The result has a value only when clock clk is true. The when keyword acts as a sampling operator. In the expression o = A(i when clk), node A is activated when clk is true, hence o is on the clock clk. Suppose that Node A multiplies its input by 10. The following table shows the behavior of the when operator.

| Instant         | 1st  | 2nd   | 3rd  | 4th  | 5th   | 6th  |

|-----------------|------|-------|------|------|-------|------|

| i               | 1    | 2     | 3    | 4    | 5     | 6    |

| clk             | true | false | true | true | false | true |

| i when clk      | 1    |       | 3    | 4    |       | 6    |

| o=A(i when clk) | 10   |       | 30   | 40   |       | 60   |

The current operator as in current(expr) gives the clock of the parent node to the flow expr. In the expression o = current(i when clk), the variable o has the clock of the parent node. The following table shows the behavior of the current operator on a small example.

| Instant    | 1st  | 2nd   | 3rd  | 4th  | 5th   | 6th  |

|------------|------|-------|------|------|-------|------|

| clk        | true | false | true | true | false | true |

| a          | 10   |       | 30   | 40   |       | 60   |

| current(a) | 10   | 10    | 30   | 40   | 40    | 60   |

Example 3 is complete program with two clocks.

**Example 3.** Root is a node with two sub-nodes. A computes x \* 10 and B computes x + 1. Node A computes at every instant whereas node B computes only on a slow clock (once over two).

```

node root(i: int) returns (oA, oB:int)

var

clk_slow: bool;

let

clk_slow = true -> not pre(clk_slow);

oA = A(i);

oB = current( B(oA when clk_slow) );

tel

```

The following table gives the value of intermediate flows and outputs:

| Instant                     | 1st  | 2nd   | 3rd  | 4th   | 5th  | 6th   | 7th  |

|-----------------------------|------|-------|------|-------|------|-------|------|

| i                           | 0    | 1     | 2    | 3     | 4    | 5     | 6    |

| oA=A(i)                     | 0    | 10    | 20   | 30    | 40   | 50    | 60   |

| clk_slow                    | true | false | true | false | true | false | true |

| oA when clk_slow            | 0    |       | 20   |       | 40   |       | 60   |

| B(oA when clk_slow)         | 1    |       | 21   |       | 41   |       | 61   |

| current(B(oA when clk_slow) | 1    | 1     | 21   | 21    | 41   | 41    | 61   |

Flow oA is the output of node A which computes i+1. The clock of oA is the same as the one of root. Expression oA when clk\_slow has a value only when clk\_slow is true. Node B is activated only when its inputs have values, hence B is activated when clk\_slow is true. The result of B is also on this clock.

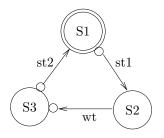

Figure 3.5: Example of Scade automaton with weak and strong transitions.

```

node root(i: int16) returns(o:int16)

let

automaton FSM

initial state S1

unless if (st1) resume S2;

let

1->pre(o) + i; -- body S1

0

tel

state S2

let

= 4->(last'o) + i; --body S2

0

tel

until if (wt) resume S3;

state S3

unless if (s2) reset S1;

let

= 8 - > pre(o) + i; - body S3

0

tel

tel

```

Figure 3.6: Example textual Scade for the automaton of Figure 3.5.

The current operator makes the output of B faster: oB is defined on the root clock. Some values are duplicated to fill the "missing" values.

In the next section, we present automata which is a formalism to express conditional executions. This is another syntax to express execution clocks for the nodes.

#### 3.1.2.2 Scade Automata

The Scade language inherits all the features of Lustre, including clock. However, it also offers an alternative feature to express conditional execution: automata.

An automaton is composed of states. For instance, the states can be initialization/nominal, degraded/performance or take off/flight/ landing. Each state has a body with some transitions to other states. In Figure 3.5, the initial state is represented with a double-circle, state with a circle and transitions with an arrow. Figure 3.6 is the same automaton in textual Scade. In Scade, only one state can be executed in the same instant. There are two kinds of transitions:

Strong transitions (st1 and st2 in the example) are represented with a circle at the start of the arrow. Conditions are evaluated before the execution of the state body. The first valid condition triggers the state change. In the textual format, the keyword unless introduces a strong transition.

Weak transitions (wt in the example) are represented with the circle on the arrow, at the same side as the point. They are evaluated after the execution of the state body. They select the next active state. The keyword until introduces a weak transition.

**Example 4.** In Figure 3.5, considering that the program starts in state S2 at the beginning of the cycle. The body of S2 is executed and weak transition wt is evaluated. If wt is triggered State S3 will be active at the next cycle. In the new cycle, if the condition of st2 is false, the body of S3 is executed. If st2 is triggered the state changes and the body of S1 is executed.

Only one transition can be triggered in the same instant, hence, if a strong transition has been triggered at the beginning of the cycle, the weak transitions are not evaluated.

**Example 5.** In Figure 3.5, if we are in S1 at the beginning of the cycle and strong transition st1 is triggered, body of S2 is executed but weak transition wt is not evaluated.

Keywords resume and reset on transitions affect the memory behavior of the state nodes. When a state is accessed with reset, the sub-nodes start in initialization, *i.e.*, the initial value is used for all the variables. For instance, in the example, if S1 is reset the value of  $\circ$  is 1. When a state is accessed with resume, the initial values of the variables are used only for the first execution.

All the variables defined outside the automaton are shared by default. For instance, i and o in Figure 3.6. There is only one state executed on the same cycle, hence there is no coherency problem. Nevertheless, it can be useful to choose between keeping them shared and using them as a local variable. To do this, there are two possibilities to access the previous value of a variable: pre(v) or last'v. With pre, the memory is local to the state, *i.e.*, the value is the one computed at the last instant when this state has been executed. With last, the memory is shared and the value is the one computed during the last instant, possibly in a different state.

Instant 1st2nd 3rd 4th 5th 6th  $7 \mathrm{th}$ 8th Executed state S2S3S1S2S3S1S2S2Value of o 2 1 4 58 1 3 9 2 3 8 init->last'o 1 4 51

4

8

1

5

2

8

**Example 6.** We compare the behavior of pre and last from the program in Figure 3.6. Variable i is 1. Executed state is given for each cycle.

For the first execution of each state (1st for S1, 2nd for S2, 4th for S3) the initialization value of o is used (1, 4 and 8). In the 1st instant, last'o is not defined. The second execution of S1 (5th instant) is triggered with a reset hence, the initialization value 1 is used for o. At the 8th instant, last'o is 3 but pre(o) is 8 (from the previous execution of S3).

We have presented some methods for representing the conditional execution of nodes: clocks in Lustre and automata in Scade . For both of them, the activation is defined by a Boolean and is not necessary regular. In the next section, we show the case of program where each node is activated regularly.

# 3.1.3 Multi-Periodic Programs

init->pre(o)

1

4

*Multi-periodic* programs are a particular case where the activation of the tasks is defined on a regular period. This is the common usage of clocks for embedded applications. Beside this activation problem, the communication has to be implemented in a way that semantics of the program are preserved.

#### 3.1.3.1 Task Activation

There are several ways to handle multi-periodic programs. The first solution is to implement the entire program on the fastest period. We obtain a program with one fast task. The slow sub-nodes

are executed conditionally according to the clock. Nevertheless, this compilation is not adapted to real-time systems since most of the time, slow (i.e. less frequent) nodes have a larger execution time than fast nodes. Another solution is to authorize the fast task to preempt the slow one. This solution is detailed in Example 7.

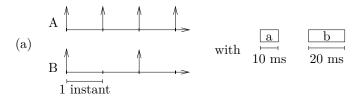

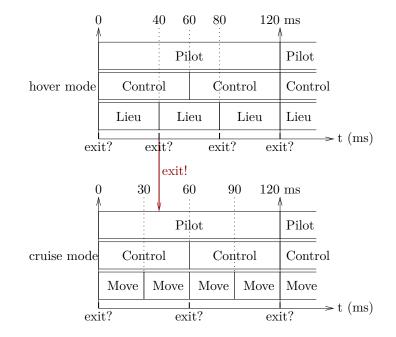

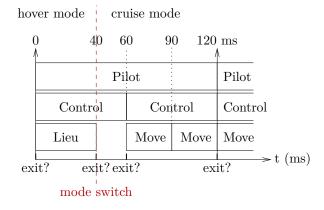

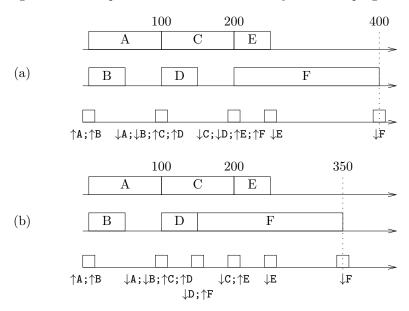

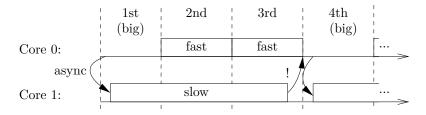

**Example 7.** Considering node A executed every period (or logical instant) and node B executed only one logical period over two (as in Example 3). As represented in Figure (a), the physical duration of A is 10 ms and the physical duration of B is 20 ms:

Schedule with preemption Execution on the fastest period

The real-time constraints of the program requires an execution period of 20 ms for A and 40 ms for B. The deadline of each task corresponds to its period. This example shows a schedule with preemption and an attempt of schedule on the fastest period.

Figure (c) shows that the execution on the fastest period 20 ms is not possible for this program since the execution time of one logical instant varies between 10 ms and 30 ms. Node A is executed every 30 ms instead of the 20 ms required in the worst case.

Intuitively, we can see that in (c), the execution time is not well balanced among the periods. As depicted in Figure (b), a solution is to split the slow node B and to execute in each period A plus half of B. Now, the duration of each period is 20 ms and B completes one period over two. As required, A completes every 20 ms and B completes every 40 ms.

This task-split can be done manually or rely on the dynamic scheduler of a real-time operating system (RTOS). The later requires the Lustre program to be compiled in a multi-task way.

Example 7 has shown a program which requires multi-tasking and preemption to meet real-time requirements. A drawback is that preemptions make the WCET estimation harder and possibly more pessimistic than the one of a plain sequential execution since it introduces context-switches and *Cache-Related Preemption Delays* (CRPD) [87].

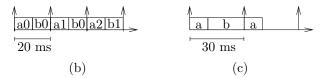

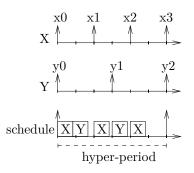

Another solution that does not rely on a preemptive scheduler is to transform the multi-periodic program into a single-period program which behaves the same. The period of this program is called hyper-period and corresponds to the smallest period for which the pattern formed by execution of the periodic tasks is repeated. It corresponds to the least common multiple of all the periods.

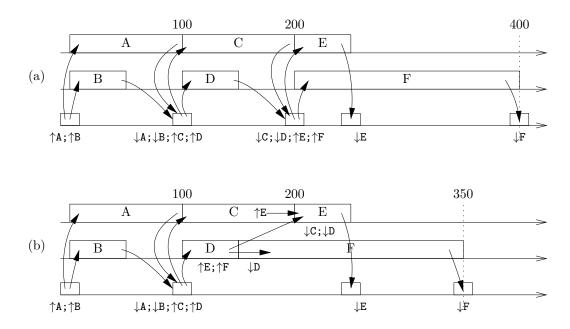

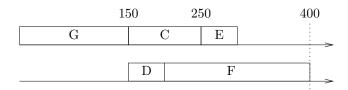

Figure 3.7 shows an example of hyper-period expansion. Task x has a period of 2 and x a period of 3. As a consequence, the hype-period is 6. On a single-core processor, the schedule of one period is x0;y0;x1;y1;x2.

Our solution relies on hyper-period expansion. Even though this method is not always optimal since it can lead to a huge hyper-period, it allows easily avoiding usage of a scheduler. It also allows avoiding splitting the tasks. When the execution is physically parallel, the preemption can be avoided since tasks of different periods can execute on different cores.

Preserving the high-level semantics of the program and determinism in a multi-task compilation is possible but non-trivial [30, 38]. In some sense the compiler is not the only responsible for implementing

Figure 3.7: Hyper-period Expansion

the semantics: the scheduler is also responsible for this implementation. This will be discussed in the next section.

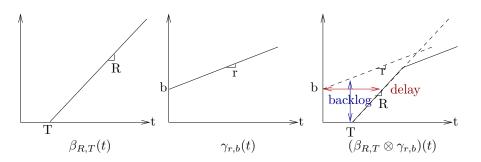

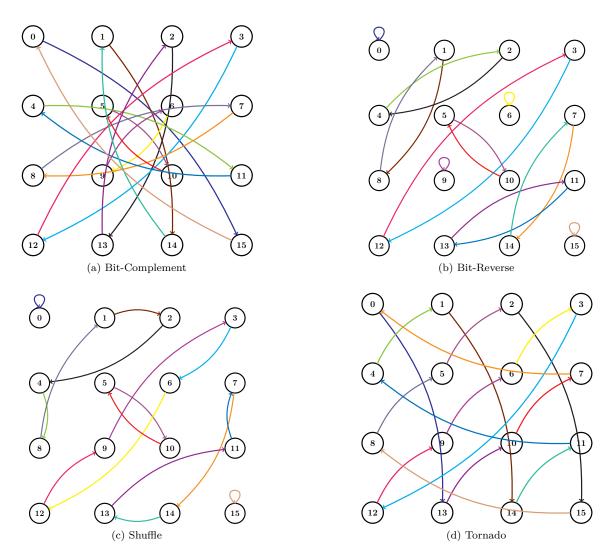

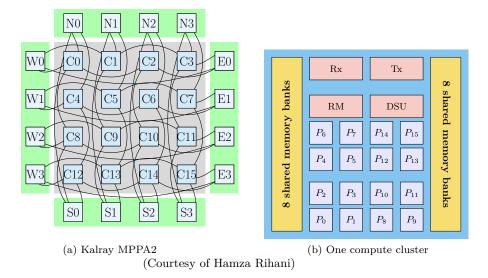

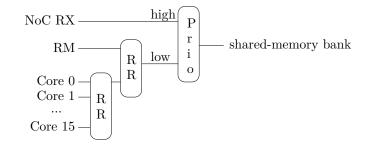

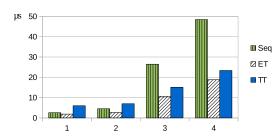

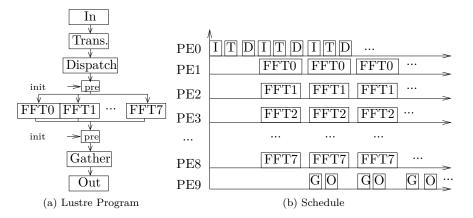

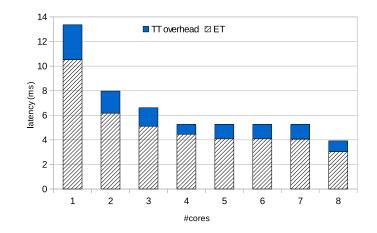

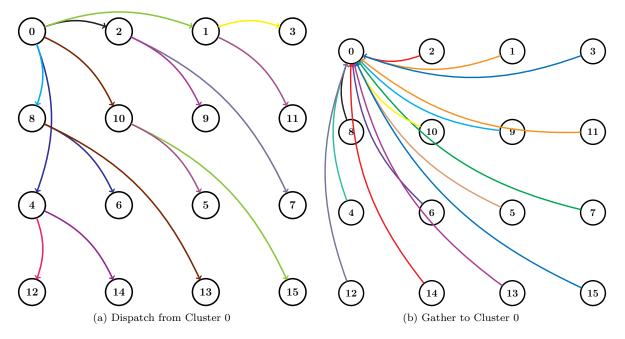

#### 3.1.3.2 Determinism of Communication