#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

#### **THESIS**

To obtain the grade of

#### **INPG DOCTOR**

Speciality:  ${\it «}$  COMPUTER SYSTEMS AND COMMUNICATIONS  ${\it »}$

(INFORMATIQUE : SYSTÈMES ET COMMUNICATION)

Prepared in the VERIMAG laboratory

Graduate school « MATHEMATICS AND COMPUTER SCIENCE » (MATHÉMATIQUES, SCIENCES ET TECHNOLOGIES DE L'INFORMATION, INFORMATIQUE)

presented and defended publicly

by

#### **Matthieu MOY**

on December, 9th 2005

#### Title:

## Techniques and Tools for the Verification of Systems-on-a-Chip at the Transaction Level

#### Supervised by

Florence Maraninchi

#### **JURY**

Gérard Michel Stephen Edwards Jean-Pierre Talpin Florence Maraninchi Laurent Maillet-Contoz President Reviewer Reviewer Director Examiner

## Acknowledgments

First of all, I would like to express my gratitude to the members of my thesis jury:

*Gérard Michel*, director of the INPG department of Telecommunications, to have accepted to be the president of my thesis jury.

Jean-Pierre Talpin, Scientific leader in INRIA Rennes and Stephen A. Edwards, assistant professor in the Computer Science Department of Columbia University, to have accepted to be reviewers for this work. To be a reviewer, for those who don't know, means reading the full document with a critical mind, look for problems and potential enhancements, and is a considerable amount of work. A wink at the first for the few anecdotes stories, reassuring (or not) about Ph.D presentations, and a special thank for the second, who is coming from New York for my presentation. Both of them gave me a few precious advices about the organization of my Ph.D document.

Laurent Maillet-Contoz, project manager at STMicroelectronics, who supervised me all along the thesis, from the definition of the subject (whereas the words "SystemC" and "TLM" did not mean anything for me!) until the last corrections of the documents, and the presentation. Once again, for those who don't know, a project manager is someone having an important load of work, with strong solicitations and short deadlines from the clients and his own manager (do "the project to be finished day before yesterday" evoke something for you?), but still, he took the time to take part in our research activities. It is in particular thanks to Laurent that we could carry out a research work with a strong link to reality.

Florence Maraninchi, Professor in Institut National Polytechnique de Grenoble to have supervised this thesis. You'll certainly feel like I'm repeating myself, but supervising a Ph.D is a big amount of work, and means a big amount of time to spend. Actually, not everybody is lucky enough to have a Ph.D director who takes the time to supervise correctly, but Florence is likes the work well done regarding this. I have learned a lot during those three years, scientifically speaking as well as regarding the way to write a paper, to increase the standing of my own work, ...

Generally, I would like to thank all the people involved in the supervising of this thesis, to have at the same time provided me the means to work and enough freedom to do a "real" Ph.D. Frank Ghenassia and Alain Clouard, respectively manager and deputy manager of the SPG team, are probably the persons to thank most for this. Some people may think that CIFRE (french thesis in cooperation with the industry) Ph.D students are not more than cheap engineers, but this is not the case with Frank and Alain. I also thank them to have given me the opportunity to meet other interesting personalities inside STMicroelectronics, such as Andrea Fedeli, specialist of formal verification tools, who kept an eye on my thesis, Marc Benveniste, interested in particular in interactive theorem proving tools, and Laurent Ducousso, who explained me the problems that his team were facing regarding the validation of designs.

I am grateful to the Verimag laboratory as a whole. It was a very pleasant framework during the three years of this Ph.D, an also the year before, for my master degree. I would cite in particular *Joseph Sifakis*, director of the laboratory, the secretaries (*Elisabeth*, *Martine*, *Valérie*, *Christine* and *Anne*, who make administrative tasks pleasant), and *Nicolas Kowalski*, the system administrator faster than his shadow, now assisted by *Jean-Noël Bouvier*.

I would like to thank equally those who made this thesis possible. *Éric Rutten* is somewhat the grandfather of this Ph.D, being the one who started discussions with STMicroelectronics, which gradually took the form of a thesis proposal. *Verimag's coffee machine*, which is to my knowledge the best tool to find a job for computer science students (whether it is to find a Ph.D or a post-doc).

Off course, I thank all my colleagues. *Laure*, friendly office neighbor, and occasionally organizer of barbecues for Ph.D students, *Jérôme*, another office neighbor, for the numerous discussions, vigorous but

nevertheless very interesting. *Romain*, the last occupant of our Verimag office, with whom I shared a few stressing moments by the end of the writing of this document ("do you plan to finish before Christmas?"). *Claude*, who, apart from the long technical discussions, made me discover the nuts beer made in Grenoble. *Alain Kauffman*, who set up a tradition of tea breaks in ST (I've been told this was not very "corporate" ...). More generally, all the members of the "synchronous" team in Verimag and SPG in ST, who would be too numerous to be enumerated.

Finally, I thank my family to have supported me in some difficult moments (if you have ever met a Ph.D student during the end of the writing of his report, you probably know what I'm talking about).

## **Contents**

| I | An approach for the Verification of Systems-on-a-Chip |                                                                                     |              |  |  |  |  |  |  |  |

|---|-------------------------------------------------------|-------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| 1 | Intr                                                  | roduction                                                                           | 11           |  |  |  |  |  |  |  |

|   | 1.1                                                   | Technical Context                                                                   | 11           |  |  |  |  |  |  |  |

|   | 1.2                                                   | General Objectives for the Thesis                                                   | 12           |  |  |  |  |  |  |  |

|   | 1.3                                                   | Work Context and Motivations                                                        | 13           |  |  |  |  |  |  |  |

|   |                                                       | 1.3.1 Motivations in the Industrial Context of STMicroelectronics                   | 13           |  |  |  |  |  |  |  |

|   |                                                       | 1.3.2 Motivations in the Academic Context of Verimag                                | 14           |  |  |  |  |  |  |  |

|   | 1.4                                                   | Approach and Technical Choices                                                      | 14           |  |  |  |  |  |  |  |

|   | 1.5                                                   | Summary of Contributions and Limitations of the Approach                            | 14           |  |  |  |  |  |  |  |

|   | 1.6                                                   | Outline of the Document                                                             | 15           |  |  |  |  |  |  |  |

| 2 | Mod                                                   | deling Systems-on-a-Chip at the Transaction Level in SystemC                        | 17           |  |  |  |  |  |  |  |

|   | 2.1                                                   | Introduction                                                                        | 17           |  |  |  |  |  |  |  |

|   | 2.2                                                   | The Systems-on-a-Chip Design Flow                                                   | 18           |  |  |  |  |  |  |  |

|   |                                                       | 2.2.1 Hardware – Software Partitioning                                              | 18           |  |  |  |  |  |  |  |

|   |                                                       | 2.2.2 Different Levels of Abstraction                                               | 19           |  |  |  |  |  |  |  |

|   |                                                       | 2.2.3 Verification, Validation, Test                                                | 21           |  |  |  |  |  |  |  |

|   | 2.3                                                   | The Transaction Level Model                                                         | 22           |  |  |  |  |  |  |  |

|   |                                                       | 2.3.1 Example of a TLM platform                                                     | 22           |  |  |  |  |  |  |  |

|   |                                                       | 2.3.2 TLM Concepts and Terminology                                                  | 22           |  |  |  |  |  |  |  |

|   |                                                       | 2.3.3 Importance of TLM in the Design Flow                                          | 23           |  |  |  |  |  |  |  |

|   | 2.4                                                   | •••••••••••••••••••••••••••••••••••••••                                             |              |  |  |  |  |  |  |  |

|   |                                                       | 2.4.1 Need for a new "language"                                                     | 24           |  |  |  |  |  |  |  |

|   |                                                       | 2.4.2 The SystemC Library                                                           | 25           |  |  |  |  |  |  |  |

|   |                                                       | 2.4.3 TLM in SystemC                                                                | 30           |  |  |  |  |  |  |  |

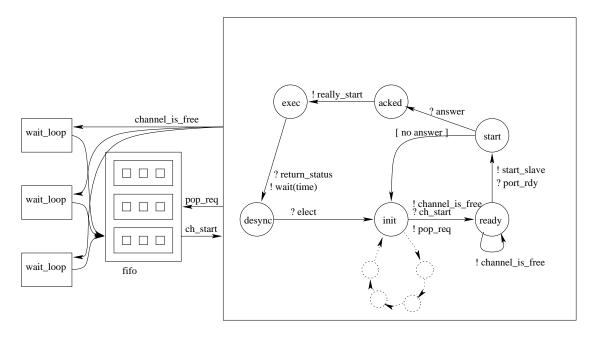

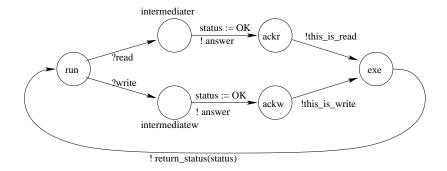

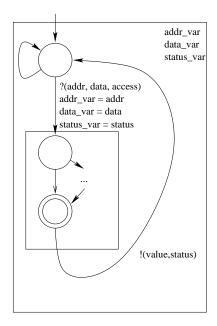

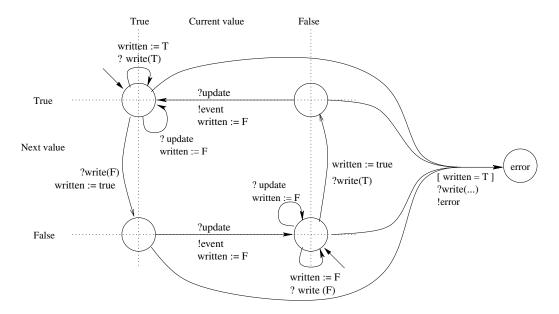

|   | 2.5                                                   | 2.5 A Larger Example: The EASY Platform                                             |              |  |  |  |  |  |  |  |

|   |                                                       | 2.5.1 Description of the Platform                                                   | 33           |  |  |  |  |  |  |  |

|   |                                                       | 2.5.2 A TLM model for EASY                                                          | 34           |  |  |  |  |  |  |  |

| 3 | Ove                                                   | erview of LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction |              |  |  |  |  |  |  |  |

|   | Leve                                                  |                                                                                     | <b>37</b> 37 |  |  |  |  |  |  |  |

|   | 3.1                                                   |                                                                                     |              |  |  |  |  |  |  |  |

|   | 3.2                                                   | Techniques and Tools for the Verification of SoCs                                   | 38           |  |  |  |  |  |  |  |

|   |                                                       | 3.2.1 Algorithms for Formal Verification                                            | 38           |  |  |  |  |  |  |  |

|   |                                                       | 3.2.2 Candidate Tools for the Verification of SoCs                                  | 41           |  |  |  |  |  |  |  |

|   | 3.3                                                   | Our Verification Approach                                                           | 42           |  |  |  |  |  |  |  |

|   |                                                       | 3.3.1 Expressing Properties                                                         | 42           |  |  |  |  |  |  |  |

|   |                                                       | 3.3.2 Synchronization Code Vs. Complex Algorithms                                   | 43           |  |  |  |  |  |  |  |

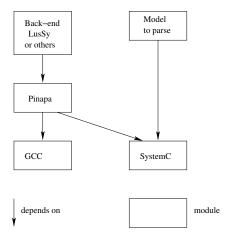

|   |                                                       | 3.3.3 The LUSSY Tool Chain                                                          | 43           |  |  |  |  |  |  |  |

| Π | Αι         | itomatic Extraction of Formal Semantics of SystemC Models                 |

|---|------------|---------------------------------------------------------------------------|

| 1 | PINA       | APA: Extracting Architecture and Behavior Information From SystemC Models |

|   | 4.1        | Introduction                                                              |

|   |            | 4.1.1 Static and dynamic information in SystemC                           |

|   |            | 4.1.2 PINAPA: Requirements                                                |

|   |            | 4.1.3 Contributions                                                       |

|   | 4.2        | Related Work                                                              |

|   |            | 4.2.1 Existing SystemC Tools                                              |

|   |            | 4.2.2 Other combinations of static and dynamic analyzers                  |

|   | 4.3        | PINAPA Principles, Limitations and Uses                                   |

|   |            | 4.3.1 Specifications of PINAPA                                            |

|   |            | 4.3.2 Limitations                                                         |

|   |            | 4.3.3 Other possible approaches                                           |

|   |            | 4.3.4 Pinapa: Current and Future Uses                                     |

|   | 4.4        | Implementation of PINAPA                                                  |

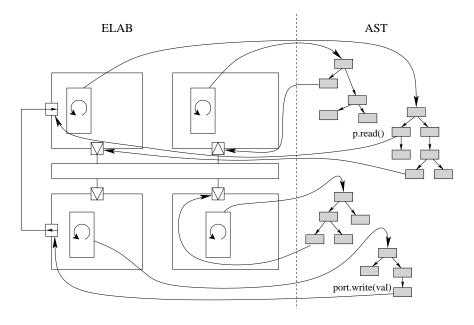

|   | 4.4        | 4.4.1 Links from ELAB to AST                                              |

|   |            |                                                                           |

|   |            | 4.4.2 Links from AST to ELAB                                              |

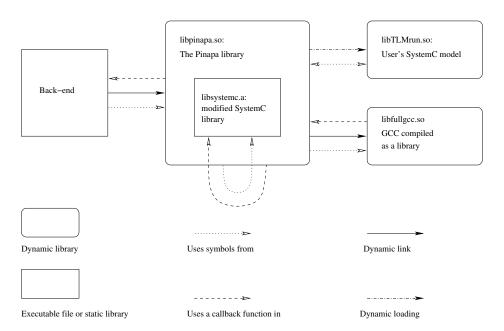

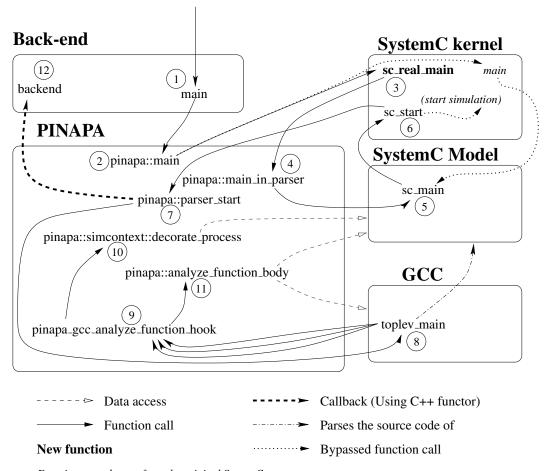

|   |            | 4.4.3 Architecture of PINAPA                                              |

|   |            | 4.4.4 Modifications of GCC and SystemC                                    |

|   |            | 4.4.5 Practical Considerations                                            |

|   | 4.5        | Parsing the EASY Platform With PINAPA                                     |

|   | 4.6        | Conclusion                                                                |

|   | HPIC       | OM: Heterogeneous Parallel Input/Output Machines                          |

|   | 5.1        | Introduction                                                              |

|   | J.1        | 5.1.1 The Need For an Intermediate Formalism                              |

|   |            | 5.1.2 Design Choices                                                      |

|   |            | 5.1.3 Contents of the chapter                                             |

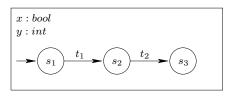

|   | 5.2        | HPIOM Basic Concepts                                                      |

|   | 3.2        |                                                                           |

|   |            |                                                                           |

|   |            |                                                                           |

|   | <b>.</b> . | 5.2.3 Non-determinism                                                     |

|   | 5.3        | Additional constructs                                                     |

|   |            | 5.3.1 Convenience constructs                                              |

|   |            | 5.3.2 Abstract Addresses                                                  |

|   | 5.4        | Expression of Properties in HPIOM                                         |

|   | 5.5        | Implementation of and Manipulation of HPIOM                               |

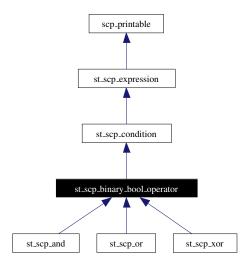

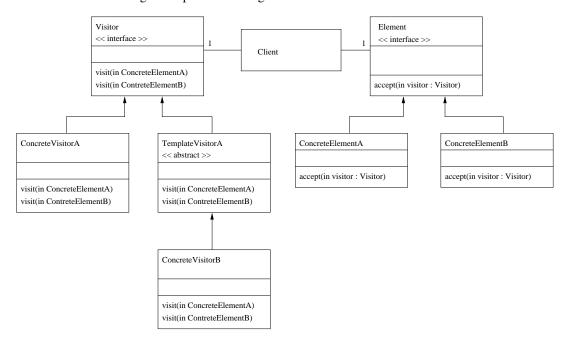

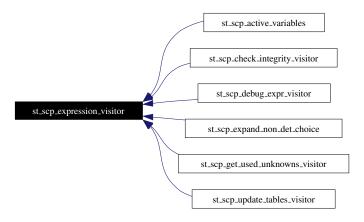

|   |            | 5.5.1 HPIOM Expressions and the Composite Design Pattern                  |

|   |            | 5.5.2 HPIOM Expressions and the Visitor Design Pattern                    |

|   |            | 5.5.3 On-the-fly Optimizations                                            |

|   |            | 5.5.4 Future improvements                                                 |

|   | Rici       | :: Semantics of SystemC and TLM Constructs in Terms of Automata           |

|   | 6.1        | Introduction                                                              |

|   | J.1        | 6.1.1 Principles                                                          |

|   |            | *                                                                         |

|   | 6.2        |                                                                           |

|   | 6.2        | Semantics of process code into HPIOM                                      |

|   |            | 6.2.1 Simple Operations and Sequence                                      |

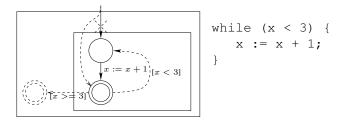

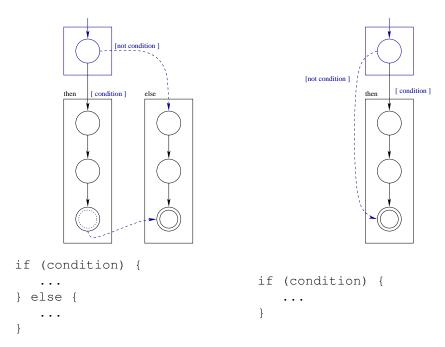

|   |            | 6.2.2 Control Structures                                                  |

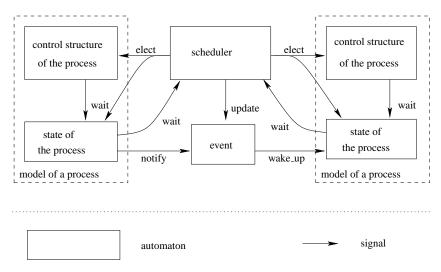

|   | 6.3        | Semantics of the Synchronization Primitives and the Scheduler             |

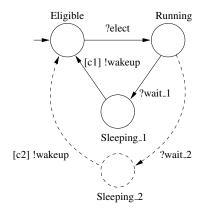

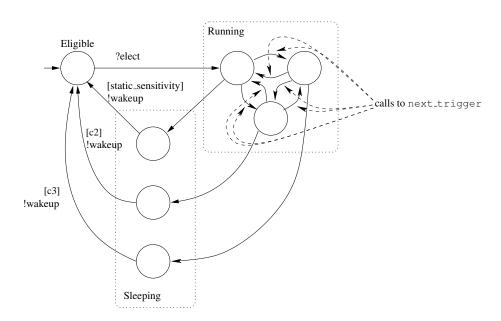

|   |            | 6.3.1 The SystemC Scheduling Mechanism                                    |

|   |            | 6.3.2 Model for the sclevent                                              |

|   | 6.4        | Communication Mechanisms                                                  |

|    |      | 6.4.1 SystemC Signal                                                                     | 98  |

|----|------|------------------------------------------------------------------------------------------|-----|

|    |      | 6.4.2 Direct Semantics of TLM Constructs                                                 | 99  |

|    |      | 6.4.3 Unmanaged SystemC Constructs                                                       | 05  |

|    | 6.5  | Encoding Properties                                                                      |     |

|    |      | 6.5.1 Assertions                                                                         |     |

|    |      | 6.5.2 Multiple write on a Signal During the Same $\delta$ -cycle                         |     |

|    |      | 6.5.3 Process Termination                                                                |     |

|    |      | 6.5.4 Mutual exclusion                                                                   |     |

|    |      | 6.5.5 Concurrent TLM Port Accesses                                                       |     |

|    | 6.6  | Related Work                                                                             |     |

|    | 0.0  | 6.6.1 Other Formal Semantics for SystemC                                                 |     |

|    |      | 6.6.2 SC2PROM                                                                            |     |

|    |      | 6.6.3 SystemC Translation Into Signal                                                    |     |

|    | 6.7  |                                                                                          |     |

|    | 0.7  | Conclusion                                                                               | .Uo |

| ** | T T  | 1                                                                                        | ΛΛ  |

| II | ΙU   | sing HPIOM for Formal Verification 1                                                     | 09  |

| 7  | BIR  |                                                                                          | 11  |

|    | 7.1  | Introduction                                                                             |     |

|    | 7.2  | Results of BIRTH on Some Examples, Without Optimization                                  | .12 |

|    | 7.3  | Semantic Preserving Transformations                                                      | 13  |

|    |      | 7.3.1 Abstract Addresses Expansion                                                       | 13  |

|    |      | 7.3.2 Non-Deterministic Choices Expansion                                                | 13  |

|    |      | 7.3.3 Reducing the Number of Variables and Inputs                                        | 13  |

|    |      | 7.3.4 Reduce the Number of States by Parallelizing Transitions                           | 17  |

|    | 7.4  | An Approximation Conservative for Safety Properties: Abstracting Away Numerical Values 1 | 18  |

|    | 7.5  | Non-conservative Approximations                                                          | 18  |

|    |      | 7.5.1 Initialize variables deterministically                                             |     |

|    |      | 7.5.2 Limit the Depth of the Proof                                                       |     |

|    |      | 7.5.3 Specify the Initial State Manually                                                 |     |

|    | 7.6  | Conclusion                                                                               |     |

| 8  | Racl | x-Ends: Connecting HPIOM to Verification Tools                                           | 21  |

| Ü  | 8.1  | Introduction                                                                             |     |

|    | 8.2  | Presentation of the Verification Tools                                                   |     |

|    | 0.2  | 8.2.1 The Lustre Tool-Chain                                                              |     |

|    |      | 8.2.2 SMV Language and Model-Checker                                                     |     |

|    | 8.3  | Encoding in LUSTRE                                                                       |     |

|    | 0.5  | 8.3.1 Encoding State Machines in a Data-Flow Language, the Case of LUSTRE 1              |     |

|    |      | 8.3.2 Encoding Variables                                                                 |     |

|    |      | 8.3.3 Encoding HPIOM Communication in LUSTRE                                             |     |

|    |      |                                                                                          | 131 |

|    | 8.4  |                                                                                          | 131 |

|    | 0.4  |                                                                                          |     |

|    |      | 8.4.1 Defining a Sequence: next Vs pre                                                   |     |

|    |      | 8.4.2 State Machines                                                                     |     |

|    |      | 8.4.3 Encoding Variables                                                                 |     |

|    |      | 8.4.4 HPIOM Communication in SMV                                                         |     |

|    | 0.7  | 8.4.5 Results of the SMV Generator for the EASY Platform                                 |     |

|    | 8.5  | CC C                                                                                     | 134 |

|    |      | 8.5.1 Validating one Back-End at a Time                                                  |     |

|    |      | 8.5.2 Comparing LUSTRE and SMV Code to SystemC                                           |     |

|    |      | 8.5.3 Comparing the Back-Ends                                                            |     |

|    | 8.6  | Tools Comparison                                                                         | 136 |

|    | 8.7                                                           | 8.6.1 Input Languages                                                               | 137 |  |  |  |  |  |  |

|----|---------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| Co | onclu                                                         | usion and Perspectives                                                              | 145 |  |  |  |  |  |  |

| 9  | <b>Con</b> 9.1                                                | clusion Context                                                                     | 145 |  |  |  |  |  |  |

|    | 9.2                                                           | Results and Discussion                                                              |     |  |  |  |  |  |  |

|    | 7.2                                                           | 9.2.1 Contributions of the Thesis                                                   |     |  |  |  |  |  |  |

|    |                                                               | 9.2.2 The Choice of SystemC                                                         |     |  |  |  |  |  |  |

| 10 | Pers                                                          | spectives                                                                           | 151 |  |  |  |  |  |  |

|    | 10.1                                                          | Possible Improvements and Uses for LusSy                                            |     |  |  |  |  |  |  |

| Aį | pen                                                           | adixes                                                                              | 155 |  |  |  |  |  |  |

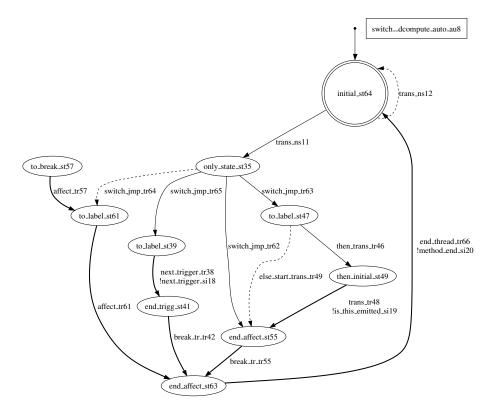

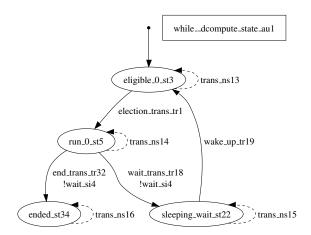

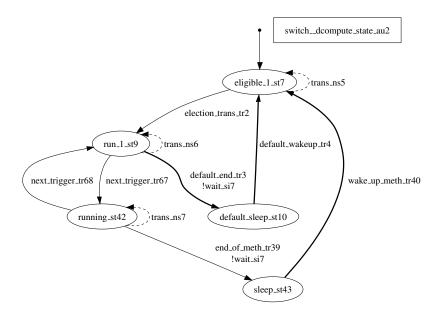

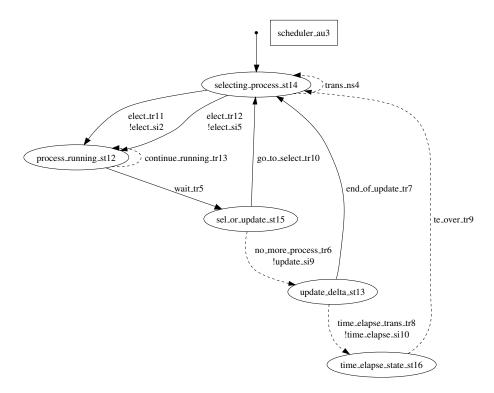

| A  | Example of translation into HPIOM: switch and while statement |                                                                                     |     |  |  |  |  |  |  |

|    |                                                               | Introduction                                                                        |     |  |  |  |  |  |  |

|    |                                                               | The platform                                                                        |     |  |  |  |  |  |  |

|    | A.3                                                           | C++ constructs                                                                      |     |  |  |  |  |  |  |

|    |                                                               | A.3.2 switch Statement                                                              |     |  |  |  |  |  |  |

|    | A.4                                                           |                                                                                     |     |  |  |  |  |  |  |

|    |                                                               | A.4.1 Processes and the Scheduler                                                   |     |  |  |  |  |  |  |

|    |                                                               | A.4.2 Communication: the Example of the sc_signal                                   | 165 |  |  |  |  |  |  |

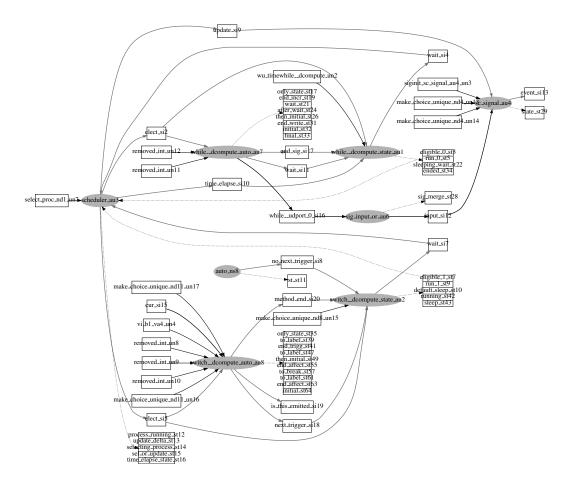

|    | A.5                                                           | Global Picture                                                                      |     |  |  |  |  |  |  |

|    |                                                               | A.5.1 Main Files                                                                    | 165 |  |  |  |  |  |  |

| В  | Why Formal Languages Should be Simple and Formal              |                                                                                     |     |  |  |  |  |  |  |

|    | B.1                                                           |                                                                                     |     |  |  |  |  |  |  |

|    |                                                               | B.1.1 Formal and Informal Languages                                                 |     |  |  |  |  |  |  |

|    | B.2                                                           | B.1.2 Formal Proof, 100% Safety?                                                    |     |  |  |  |  |  |  |

|    |                                                               | A Higher Level Language: SMV                                                        |     |  |  |  |  |  |  |

|    | B.4                                                           |                                                                                     |     |  |  |  |  |  |  |

|    | <b>D</b> . 1                                                  | B.4.1 The Problem                                                                   |     |  |  |  |  |  |  |

|    |                                                               | B.4.2 Trying to Understand                                                          |     |  |  |  |  |  |  |

|    |                                                               | B.4.3 Consequence on LUSSY                                                          |     |  |  |  |  |  |  |

|    | B.5                                                           | Executability and Determinism: a Way to Clarify the Semantics of Informal Languages | 175 |  |  |  |  |  |  |

|    | B.6                                                           | Conclusion                                                                          | 175 |  |  |  |  |  |  |

| Bi | bliog                                                         | graphy                                                                              | 182 |  |  |  |  |  |  |

| In | dov                                                           |                                                                                     | 183 |  |  |  |  |  |  |

## Part I

# An approach for the Verification of Systems-on-a-Chip

### **Chapter 1**

### Introduction

#### Contenu

| <br> |                                                                   |    |  |  |  |

|------|-------------------------------------------------------------------|----|--|--|--|

| 1.1  | Technical Context                                                 | 11 |  |  |  |

| 1.2  | General Objectives for the Thesis                                 |    |  |  |  |

| 1.3  | Work Context and Motivations                                      | 13 |  |  |  |

|      | 1.3.1 Motivations in the Industrial Context of STMicroelectronics | 13 |  |  |  |

|      | 1.3.2 Motivations in the Academic Context of Verimag              | 14 |  |  |  |

| 1.4  | 1.4 Approach and Technical Choices                                |    |  |  |  |

| 1.5  | Summary of Contributions and Limitations of the Approach          | 14 |  |  |  |

| 1.6  | Outline of the Document                                           | 15 |  |  |  |

|      |                                                                   |    |  |  |  |

#### 1.1 Technical Context

In 1980, Gordon Moore, Engineer at Fairchild Semiconductor, one of the two co-founders of Intel, stated a law according to which the number of transistors on silicon chips was doubling every eighteen months. Although it is not a real physical law, this prediction revealed to be incredibly exact. Between 1971 and 2001, the density of transistors actually doubled every 1,96 years. As a consequence, electronic devices became more and more powerful and less and less costly.

Surprisingly, this evolution was accompanied by a miniaturization quite as continuous. The supercomputers of the 1960's filled in a complete room, weighted several tons, for a computing capacity of only a few thousands of instructions per second. The ATLAS, for example, was the most powerful computer in the world in 1964, with two hundred thousands of instructions per second. This order of magnitude of computing power gradually became the standard for micro-computers, calculators, and more and more miniature objects which are now part of our daily life.

While it has been possible to envisage a miniaturization of the computers for a long time, very few people had imagined that the miniaturization would reach such a point. In March 1949, for example, the magazine "popular mechanics" wrote: "Where a calculator like the ENIAC today is equipped with 18,000 vacuum tubes and weighs 30 tons, computers in the future may have only 1,000 vacuum tubes and perhaps weigh only 1.5 tons.".

Today, the specialists in the domain think that nothing should prevent Moore's law from continuing for at least the next 10 years. If the current evolution is extrapolated, the size of a transistor should reach the scale of the atom in the years 2020. It is probable that Moore's law cease to apply at this point. The speed of computers will then either stagnate, or leap forward with the arrival of quantum computers.

While the physical limits of miniaturization and computing speed appear to be far from being reached, other significant limitations are already coming into the picture today. The number of transistors, the size of the memories, the frequency of the chips grow in an exponential way with time but other parameters are also growing in the same proportions. For instance, the cost of a micro-electronics factory, the fixed costs

for the manufacture of a chip, and its electric consumption are also growing exponentially with time. This growth is mainly compensated by the growth of the market, which allows to share the fixed costs between a larger number of chips, so that the total cost of each of them remains reasonable, but one should not neglect that the growth of the market cannot be infinite.

Another limitation is the amount of code that the designers are able to write in a reasonable time. Being able to increase the number of transistors on a chip is really interesting only if one is also able to write the code which once synthesized, will give the organization of these transistors on the chip. With traditional techniques, the productivity of the designers increases by only 30% a year, whereas the number of transistors can increase by 50%. Without major innovation, the difference between the productivity of the design and the capacity of the chips would thus increase approximately 20% per year. This divergence is generally referred to as the "design gap".

New techniques must consequently be set up continuously to fill in this gap. Tools for automatic synthesis for the Register Transfer Level (RTL) to the gate-level have been a real revolution, but is not sufficient anymore today.

The repartition of the functionalities between software and hardware solves part of the problems of the "design gap". It makes it possible to re-use the same chip in different contexts, thus sharing the fixed costs between several projects. Programmable generic components, ranging from the entirely generic processor to the DSP (Digital Signal Processor) and including the micro-controllers, can be used to design the chip. It is generally admitted that a given functionality is approximately implemented ten times faster in software than in hardware (but on the other hand, the performances of the software are not as good as ones of hardware).

A new category of systems has been emerging during the last few years, including one or more processors, dedicated components and input/output modules, the whole fitting on a single chip. In other words, current technologies make it possible to implement in a single chip the equivalent of the contents of a computer motherboard. These systems are called *System-on-a-Chip* (SoCs).

The design of a System-on-a-Chip is thus a joint development of software and hardware. The hardware only makes sense with its corresponding embedded software, and the software needs the hardware to run. The constraints of the market force the development cycle of a chip to remain as short as possible, and it is not acceptable to wait for the chip to physically exist to start the development of the corresponding software. The development of the software has therefore to be carried out, or at least started, on a simulator.

A solution would be to use the synthesizable version of the hardware part of the chip as a simulator on which to develop the embedded software. This approach (RTL simulation) is used in some contexts, but the slowness of simulation does not allow scaling up. Moreover, this approach does not make it possible to start the development of the software before the code for the synthesizable version of the hardware is written.

The reason for which the simulation of the synthesizable model is so slow is that the level of abstraction used (Register Transfer Level, or RTL) includes too many details of implementation, of protocols, which are not relevant for the software. This led recently to the introduction of a new level of abstraction, called *Transaction Level Modeling* or TLM, in which only what is necessary for the software to run is modeled. At this level, a platform is a set of modules connected by communication channels. The communication channels transport transactions, which are an atomic exchange of data between two modules, whose size can vary, and is in general unrelated to the size of the bus.

The transaction level models must appear early in the design flow of a circuit, and become the reference models for the following developments. The reliability of these models is thus particularly important. As many bugs as possible must be found, as soon as possible. The systems considered are usually not "critical" systems in the sense that the price of each bug is counted in human lives, but are systems for which the price of a bug is counted in millions of dollars.

#### 1.2 General Objectives for the Thesis

The most general objective of the thesis is to develop methods and tools to increase the reliability of the chips by using the transactional models. Since TLM to RTL synthesis is believed to be infeasible automatically and efficiently, the ideal product would be a formal comparison tool for TLM and RTL

models. Such a tool would be extremely complex to develop both theoretically (to compare two programs which use different concepts is a very difficult problem) and practically (one would need extraction tools for both the TLM *and* the RTL levels).

Within the framework of a thesis (three man.year), it seemed much more reasonable to concentrate on the transaction level, and to keep the questions of comparisons with lower abstraction levels for possible future works. The objective of this thesis will thus be to check properties on the transaction level model, independently of the levels of abstraction into which these models will be refined. Since TLM models become the reference models for future development and validation, ensuring properties on TLM models has consequences on the reliability of the final product.

Our idea is to start implementing a set of reusable building blocks, common denominators of any tool handling the transactional models. A first application of this tool chain will be the formal verification of transactional models by existing model-checking and abstract interpretation tools, as described in the final chapter of this document. Other applications could be added thereafter.

#### 1.3 Work Context and Motivations

This document presents the work carried out on the verification of transactional models, as part of a CIFRE Ph.D (Industrial Conventions of Training by REsearch) between the "System Platform Group" (SPG) team of STMicroelectronics and the "Synchronous Languages and Reactive Systems" team of the Verimag laboratory, between October 2002 and December 2005.

It was the first thesis in co-operation between these two teams, and the first year of co-operation between STMicroelectronics and Verimag. The interest was thus not only the scientific contents of the thesis, but also the creation of links between these two teams, which became one of the basis for a more durable co-operation between STMicroelectronics and Verimag. Indeed, two other Ph.D students (Claude Helmstetter and Jérôme Cornet) joined the project and are working on related subjects. A common laboratory between Verimag and STMicroelectronics is being created, as well as a Minalogic (a competitiveness center dedicated to software for micro and nanotechnologies) project called OpenTLM.

The first stage was to understand the principles of the transaction level from a theoretical point of view. From the point of view of STMicroelectronics, the development infrastructure for transactional models is mainly guided by the immediate needs of the users. From a "research" point of view, it is important to make sure that these developments are done on solid theoretical bases. The questionings raised by works on the tool Lussy, for example, helped us to understand the concepts of asynchronous execution and time in SystemC, and contributed to the development of coding directives for the models with a notion of time: the distinction between the levels "Programmer View" and "Programmer View plus Timing" presented in the next chapter (section 2.2.2.2).

#### 1.3.1 Motivations in the Industrial Context of STMicroelectronics

For the SPG team of STMicroelectronics, the general objective is to create a complete development environment for models at the transaction level, based on SystemC. Before the beginning of the thesis, SystemC components to model abstract communication channels had already been developed, as well as a prototype of configuration management and build system to simplify the task of the users. Meanwhile, these tools evolved. Bridges between various languages and protocols, a finer definition of the various levels of abstraction inside the transaction level, the integration of tools and simulators commercial, etc... were added.

A number of these improvements are short-term evolutions developed as a response to user requests. In parallel, a longer-term approach, in co-operation with public laboratories, aims at improving methodologies, and anticipating future problems. The co-operation with the Verimag laboratory is a way to have formal methods applied to concrete problems. One of the motivations for the strong presence of STMicroelectronics in the region of Grenoble is to benefit from its rich scientific environment.

#### 1.3.2 Motivations in the Academic Context of Verimag

The Verimag laboratory has both a number of tools and a very good qualification level regarding program verification. The laboratory, and the synchronous team in particular, tackles at the same time rather fundamental research topics and industrial research ones.

A necessary condition to make good quality applied research is the availability of real case studies. One of the motivations to study the transaction level modeling could be that a publication seems to have more chance to be accepted if it contains key words like "TLM" or "System-on-a-Chip" for example, than if it deals only with automata, or Moore or Mealy machines. We do not intend to take a theoretical problem and try to convert it into an applied research topic by only adding some appreciated keywords that the industry likes. Our starting point is actually a concrete problem to solve, and the way to do it is to look for techniques applicable to it. The fundamental research topics make it possible to solve problems from industrial research, and the case studies give the direction to be followed for the more theoretical questions.

For Verimag, a co-operation with STMicroelectronics is a way to understand the design flow of Systems-on-a-Chip, from the inside.

#### 1.4 Approach and Technical Choices

One of the characteristics of the problem which we are dealing with here is that we control neither the language (SystemC is defined by a consortium on which we have only little influence), nor the execution model (which is part of SystemC).

A solution could have been to study the execution model of SystemC, to redefine it in terms of automata or another well known formalism, and to work directly and only on this formalism. This solution is not very satisfying since it does not make it possible to test the approach directly on real case studies in an automatic way.

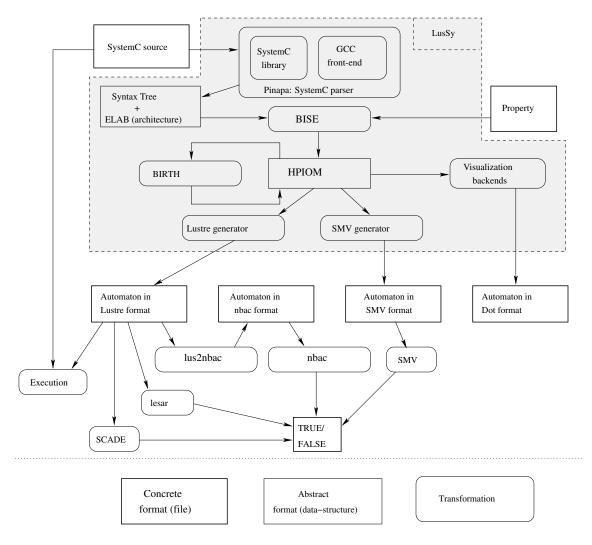

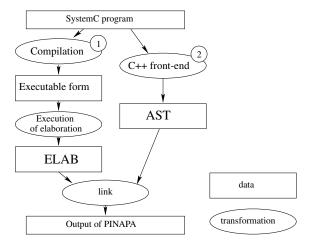

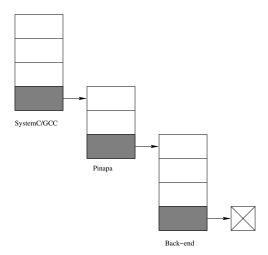

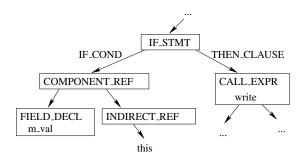

A significant part of this work is thus the design and implementation of extraction tools. It is a mandatory first step for any formal work exploiting the characteristics of a new language. This extraction is done in two phases: A "syntactic" extraction, which is a little particular in the case of SystemC, and a "semantic" extraction. The one first is implemented in the tool PINAPA. It is already re-used in projects of STMicroelectronics and other external research projects. The second one, implemented in the component BISE of the tool LUSSY, could also be re-used in future work. The task of BISE can be summarized with a transformation of the output of PINAPA, which is a strongly decorated syntactic tree representing the SystemC program, into a simple and well defined structure of automata.

A series of transformations is then applied. Some are generic, others are specific to the models we analyze. Some are exact transformations, others are abstractions. This is implemented in the component BIRTH.

The last stage is to generate code for the external tools on which we rely for the proofs themselves. We can today use all the tool chain of the LUSTRE [BCH<sup>+</sup>85] language, as well as the tool SMV [McM01, McM93].

The tool LUSSY was entirely designed and implemented during this thesis. Some parts were carried out with the assistance of students in second year of engineering school (Cédric Bonnot and Remi Emonet), and a master thesis student (Muzammil Muhammad Shahbaz).

Our approach is similar to those of traditional compilers, with a front-end part, intermediate transformations, and a code generator. This approach allows us to have extremely few theoretical limitations, at the syntactical as well as at the semantic level (in practice, some constructs were not useful for us and were not implemented, but they could be easily so if necessary).

#### 1.5 Summary of Contributions and Limitations of the Approach

The main contributions of this thesis are:

A method to extract information from a SystemC model and an implementation of this method called PINAPA. We will see how SystemC is different from traditional languages, and how a SystemC

front-end should be different from a usual compiler front-end. The approach followed for PINAPA has no published equivalent to the best of our knowledge.

**An executable formal semantics for TLM models** written in full SystemC, with an operational translation tool; The output of this tool is reusable for other purposes.

A way of expressing safety properties in SystemC without the help of a new language;

**An intermediate formalism,** HPIOM, with a set of transformations and optimizations. This intermediate representation can, and will probably be used outside LUSSY, as an intermediate format between some of Verimag tools.

**A working connection to several verification tools.** This allowed us to prove some properties on small platforms, and provided an interesting benchmark comparing the verification tools.

The tool LUSSY is still in prototyping phase. Some C++ or SystemC constructs have not yet been taken into account, by lack of time, but could be added without real theoretical problem. As opposed to this, the approach followed presents some intrinsic and theoretical limitations that would be much harder to work around:

**Extraction of information from SystemC** is a difficult problem, not only to solve, but also do define in the general case. We will see how, in the case of a program using dynamic data-structure to access SystemC objects, it doesn't really make sense to try to find the SystemC object represented by a given variable. PINAPA uses an approach that avoids most of the limitations present in similar tools, but can not make the link between variables of the program and SystemC objects in this case.

The HPIOM formalism is limited in terms of expressiveness. We had to take some design decisions and find the trade-off between expressiveness and possibilities regarding formal and automatic proofs for this formalism. We have chosen a simple automata formalism. The control structure is fixed, dynamic process creation is not allowed, and the variables of the automata can not contain complex data-structures. If the source program uses dynamic data-structures, recursive function calls, etc. then the translation will have to lose some information. This loss of information is done in a conservative way for safety properties, except in the case of function calls with side effects.

**Translation from SystemC into HPIOM** also introduces, optionally, a number of approximations preserving safety. They improve the performance of the proof engine, but prevent some properties from being proved.

State explosion in the proof engine is actually the main limitation regarding the use of LUSSY for formal verification. On medium size platforms like EASY presented in section 2.5, LUSSY is able to perform the complete translation and can generate either LUSTRE or SMV, but in both case, no property could be proved. However, LUSSY provides all the building blocks to apply other proof techniques, such as modular model-checking, that could allow scaling up better.

#### 1.6 Outline of the Document

This document is divided into three parts:

I. An approach for the Verification of Systems-on-a-Chip: This first part gives a general vision of the concept of transaction level models, and possible formal approaches for their verification. Chapter 2, "Modeling Systems-on-a-Chip at the Transaction Level in SystemC" introduces the transaction level, and the SystemC implementation we're interested in thereafter. Chapter 3, "Overview of LusSy: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level" presents our verification approach as well as the alternatives. One also finds there a short presentation of the tool LusSy, his components and the way in which they are organized.

- II. Automatic Extraction of Formal Semantics of SystemC Models: In this second part, the extraction we used are presented. Chapter 4, "PINAPA: Extracting Architecture and Behavior Information From SystemC Models" presents the first component, whose role is similar to the one of a compiler front-end, for SystemC programs. Chapter 5, "HPIOM: Heterogeneous Parallel Input/Output Machines", presents the intermediate structure we use to represent the semantics of SystemC. The translation itself is detailed in chapter 6, "BISE: Semantics of SystemC and TLM Constructs in Terms of Automata", which transforms the output of PINAPA into HPIOM.

- III. Using HPIOM for Formal Verification: This part presents the use of the data extracted from the formal checking. Initially, a series of transformations is applied to the generated automata, as presented in chapter 7, "BIRTH: Back-end Independent Reduction and Transformations of HPIOM". Finally, chapter 8, "Back-Ends: Connecting HPIOM to Verification Tools" introduces the generation of LUSTRE and SMV code, which makes it possible to use model-checkers, abstract interpreters and SAT solvers to prove properties on the models. A comparison between these various tools is provided.

**Conclusion:** The last part is the conclusion, and presents the perspectives.

The attentive reader will notice that no chapter is dedicated to bibliography. Indeed, the topics treated in the various chapters are different, and we preferred distributing the bibliographical references and related works in each chapter. Similarly, the implementation of the tool LUSSY is described all along the document, and not in a dedicated part.

### **Chapter 2**

## Modeling Systems-on-a-Chip at the Transaction Level in SystemC

| Introd                      | luction                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| The S                       | ystems-on-a-Chip Design Flow                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.2.1                       | Hardware – Software Partitioning                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.2.2                       | Different Levels of Abstraction                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.2.3                       | Verification, Validation, Test                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| The T                       | ransaction Level Model                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.3.1                       | Example of a TLM platform                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.3.2                       | TLM Concepts and Terminology                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.3.3                       | Importance of TLM in the Design Flow                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.4 SystemC and the TLM API |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.4.1                       | Need for a new "language"                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.4.2                       | The SystemC Library                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.4.3                       | TLM in SystemC                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

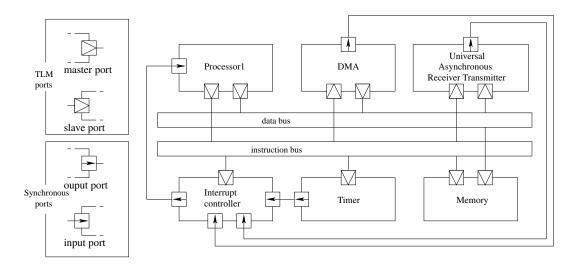

| A Lar                       | ger Example: The EASY Platform                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.5.1                       | Description of the Platform                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2.5.2                       | A TLM model for EASY                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                             | The S 2.2.1 2.2.2 2.2.3 The T 2.3.1 2.3.2 2.3.3 Syster 2.4.1 2.4.2 2.4.3 A Lar 2.5.1 | The Systems-on-a-Chip Design Flow       18         2.2.1 Hardware – Software Partitioning       18         2.2.2 Different Levels of Abstraction       19         2.2.3 Verification, Validation, Test       21         The Transaction Level Model       22         2.3.1 Example of a TLM platform       22         2.3.2 TLM Concepts and Terminology       22         2.3.3 Importance of TLM in the Design Flow       23         SystemC and the TLM API       24         2.4.1 Need for a new "language"       24         2.4.2 The SystemC Library       25         2.4.3 TLM in SystemC       30         A Larger Example: The EASY Platform       33         2.5.1 Description of the Platform       33 |  |  |  |  |

#### 2.1 Introduction

Quality and productivity constraints in the development tools for the design of embedded systems are increasing quickly. The physical capacity of chips can usually grow fast enough to satisfy those needs: The evolution of the number of transistors on a chip has been following Moore's law (growth of 50% per year) for decades, and should keep on following it for at least 10 years. But one of the design flow bottlenecks is the design productivity: with traditional techniques, it grows only by around 30% per year, leaving a gap, increasing by 20% per year between the capacity of the chips, and the amount of code the designers are able to write. This problem is often referred to as the *design gap*. New techniques have to be settled continuously to be able to fill in this gap.

This chapter will first present today's design flow, with the different levels of abstraction used to describe a chip (section 2.2). Then, we will detail the *Transaction Level Modeling* level of abstraction that will be studied in this document (section 2.3), and present the way it is implemented in SystemC (section 2.4.3). The chapter ends with a small case study: The EASY platform, in section 2.5.

#### 2.2 The Systems-on-a-Chip Design Flow

One of the past technological revolution in the hardware domain has been the introduction of the *Register Transfer Level* (RTL) to replace the *gate-level* as an entry point for the design flow. The gate-level description uses only the simple logic operators (*and*, *or*, *not*, ...) to describe the design, whereas the RTL level allows the notion of register (one-word memory), and a data-flow description of the transfers between registers at each clock cycle. Since the translation between RTL and gate-level descriptions can be done automatically and efficiently, the gate-level description is today mainly an intermediate representation synthesized from the RTL code, used for the chip manufacturing, but seldom written by hand (we can compare the role of the gate-level description in the chip design flow with the role of the assembly language in the compilation of software).

#### 2.2.1 Hardware – Software Partitioning

Raising the abstraction level above the gate-level has been a real progress, but is not sufficient to fill in today's design gap. It is necessary to maximize the reusability of the chip components, usually called *Intellectual Properties* (IPs). This can be achieved by using software components instead of *Application Specific Integrated Circuits* (ASIC).

Software components can be easily reused, modified at all steps of the design flow (a bug can be fixed or a feature can be added even after the device has been sold to the final customer). On the other hand, they are much less efficient both in terms of computation time and in terms of power consumption.

Therefore, designers need to find the compromise between software and hardware: implement the performance-critical operations using dedicated hardware components, and the non-critical parts using software. Deciding which feature will be implemented in software and which one will be implemented in hardware is called *hardware/software partitioning*. The result is a mixture of software and hardware, intermediate between general purpose CPU and ASIC and containing several components executing in parallel. It is called a *System-on-a-Chip*.

Since one of the main tasks of the embedded software is to program the hardware components, the software, or at least its low-level layers, will be highly hardware-dependent, and will not run unmodified on a standard computer. There are mainly two ways to execute such software: 1) execute it on the physical chip, and 2) execute it on a simulator.

The first option is not acceptable during the development because of time-to-market constraints: the software needs to be finished and validated a few weeks after the chip comes out of the factory. Furthermore, developing embedded software can help in finding bugs in the hardware, and the cost of a bug discovered on the physical chip is several orders of magnitude higher than a bug found before manufacturing the first chip: the first step of the manufacturing is to build the mask that will be used for the lithography of all chips. Any non trivial bug fix needs a complete rebuild of the mask, which costs around one million dollars (the cost of masks tends to grow exponentially with time, so we can't expect this problem to be solved by itself in the next few years).

The "trivial" way to simulate the hardware part of the chip is to use the RTL description. Unfortunately, due to the highly parallel nature of hardware, simulation of a large RTL design is extremely slow. It is possible to replace some components of an RTL simulation by a simulator, typically written in C, to increase the simulation speed. A common technique is to replace the processor by an instruction set simulator (ISS), and the memory by a simple array. This technique, mixing behavioral and RTL components is called cosimulation.

The next step is to get rid of RTL components and clocks completely. This raises the level of abstraction above the RTL. An emerging level of abstraction is the *Transaction Level Model (TLM)*, and will be detailed later.

Hardware devices dedicated to RTL simulation also exist (hardware accelerators, or hardware emulators based on programmable hardware like FPGA). See for example [GNJ<sup>+</sup>96]. They are extremely costly and offer very few or no debugging capabilities. They are usually used to run a large test-bench in batch mode, but not for interactive debugging.

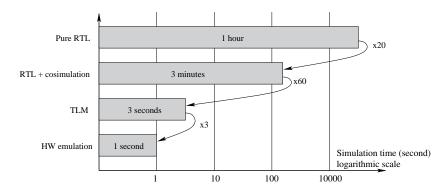

Figure 2.1 shows the simulation time we get on the same computation with those different techniques.

Figure 2.1: Simulation time for the encoding + decoding of one image in a MPEG4 codec

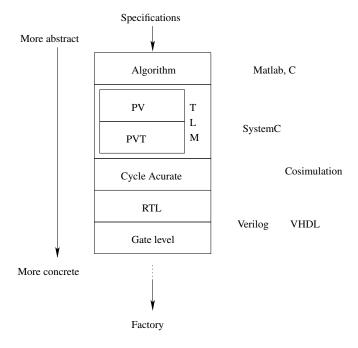

Figure 2.2: Illustration of the Different Levels of Abstractions

#### 2.2.2 Different Levels of Abstraction

This section details one by one the different levels of abstraction used to describe hardware. Ideally, the design flow should start by the highest level, and refine, either automatically or manually to the lowest level. Figure 2.2 illustrate the relationship between the different levels of abstraction. On the left are the levels of abstractions, and on the right are examples of commonly used technologies at this level of abstraction. On this picture, the ideal design flow starts from the top and refines to the bottom.

The distinction between those levels of abstraction is widely (but not quite universally) accepted. Of course, some intermediate levels can be added. See for example [Pas02] (written by an STMicroelectronics employee) or [CG03]. The way to implement them is still subject to discussion, although a standardization effort is ongoing.

#### 2.2.2.1 Algorithm

The highest level (below the specification) is the algorithm. For multimedia devices, at least part of the algorithm is provided by a norm, and reference implementations often exist. Algorithms are usually designed in high level programming languages, such as Matlab<sup>TM</sup>, or in C. At this level, the notion of software or

hardware components does not exist, and the notion of parallelism is not yet taken into account.

#### 2.2.2.2 Programmer View: PV

Then comes the Transaction Level Model, which actually splits into two flavors: the *Programmer View* (PV), and the *Programmer View plus Timing* (PVT).

At this level, the chip is modeled as a *platform* made of several *modules*. Each module shows to the external world all its functionalities, and only its functionalities. The timing aspects, for example, are not yet taken into account.

Communication between modules is done through a model of interconnect (the *interconnect* itself is the set of channels existing on the chip), made of one or several *communication channels*, whose role is to route a piece of data from a module to another one. This exchange of data is called a *transaction*.

At this level, the size of a transaction is not necessarily related to the data-width of the bus (which is not necessarily known when the PV platform is written). For an image processing algorithm, for example, the PV model can decide to transmit the data line by line, block by block, or even image by image.

An important part of the PV level is the system synchronization. At this level of abstraction, we have no real notion of timing, so the system is mostly asynchronous. A set of independant processes could hardly give a consistant behavior. For example, when a process needs a piece of data that is the output of another process, we have to ensure that the value will be produced before being used. The communication channels are not only usefull to transmit data from one module to another, but can also be used for the system synchronization. Some channels can also be dedicated to synchronization and transmit no data. This is the case for the model of an interrupt signal. It can be modeled as a boolean signal (we will observe the edges of the value, but not the value itself), or even a channel without value.

At this level of abstraction, the *model* contains all the necessary and only the necessary information to run the embedded software (thus its name).

The organization of the program is completely different from the one of the algorithmic level. The first partitioning is done, the algorithms are parallelized, even if the decision of implementing some blocks in hardware or software is not necessarily taken (since hardware/software partitioning is done based on the results of performance analysis, and since the PV level does not take performance into account, we still miss some information). Some tools can help taking partitioning decisions, and some code can be reused, but an automatic translation from the algorithm level to the PV level can not exist.

#### 2.2.2.3 Programmer View plus Timing: PVT

While TLM was originally created to ease the development of embedded software, it also proved to be useful for preliminary performance analysis. Since the TLM model contains less details than the RTL, it can be written faster (it is usually admitted that a PV model can be written ten times faster than its RTL equivalent), and should be available earlier than the RTL in the life cycle of a chip. It is therefore reasonable to use it to take decisions about the RTL design (identify the bottlenecks, dimension the modules and communication channels).

Unfortunately, the PV level does not contain the timing information necessary to perform such analysis. It is therefore necessary to enrich the PV model with timing information, with some constraints: The functionality of the PV model must not be modified (the functional equivalence between PV and PVT must be correct-by-construction as much as possible), and the effort to write the PVT model based on the PV model must be as low as possible, and in particular, lower than the effort to write a PVT model from scratch.

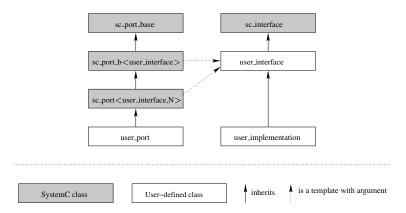

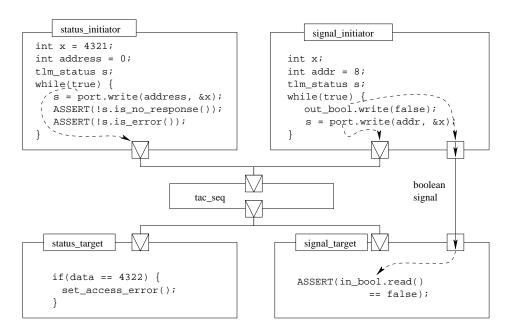

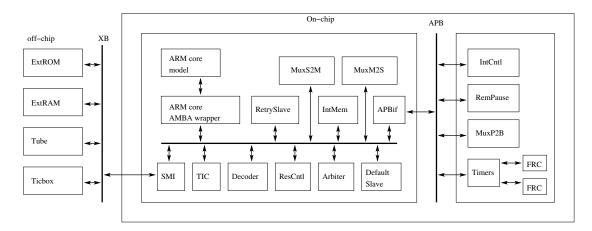

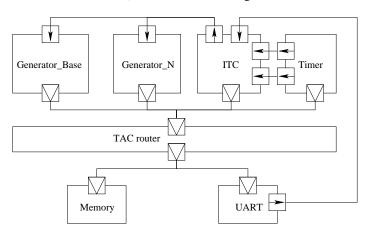

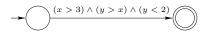

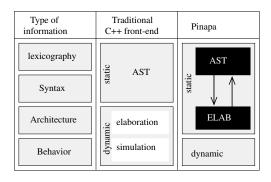

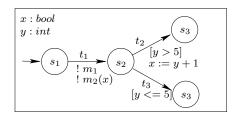

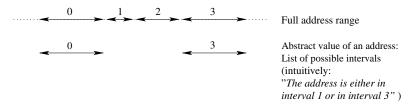

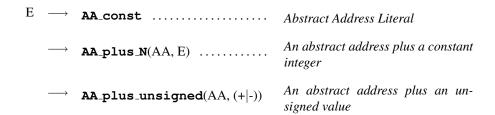

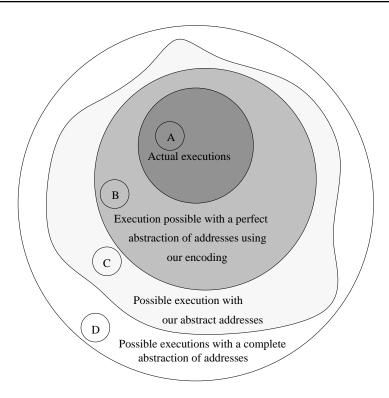

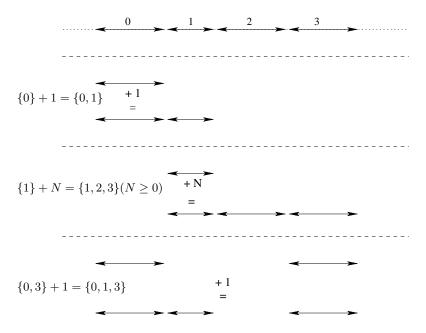

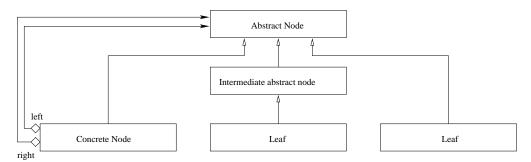

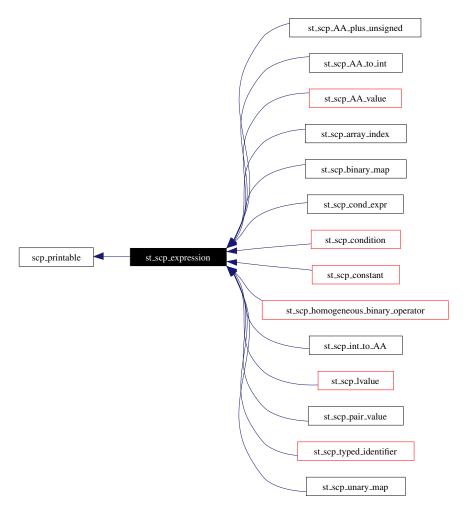

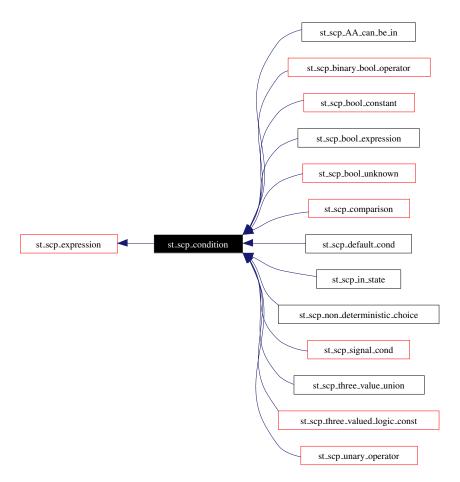

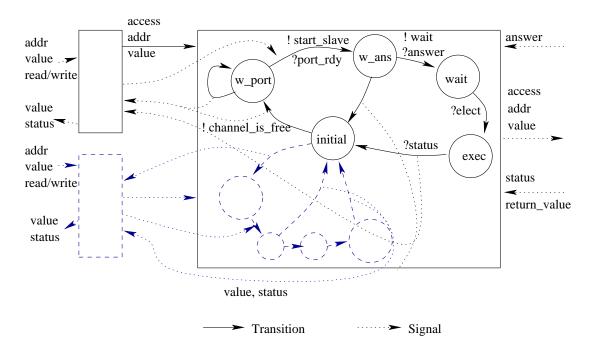

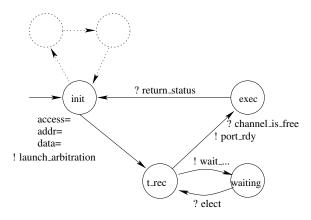

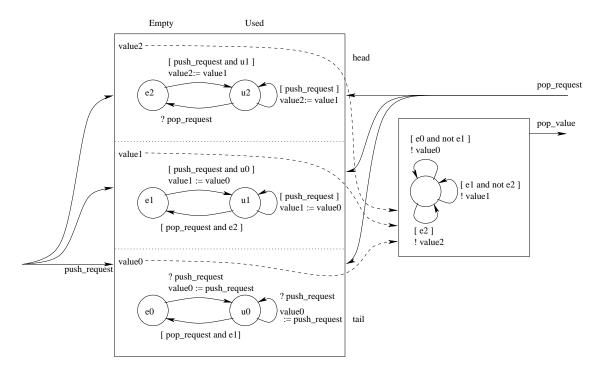

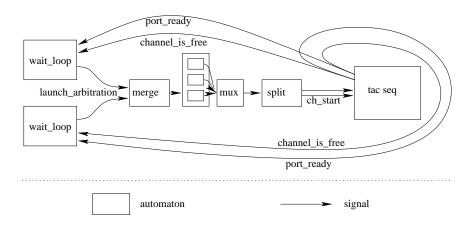

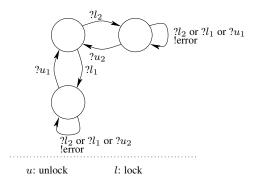

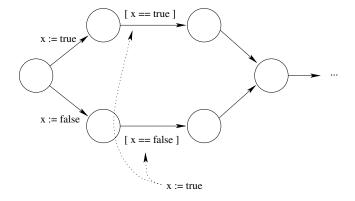

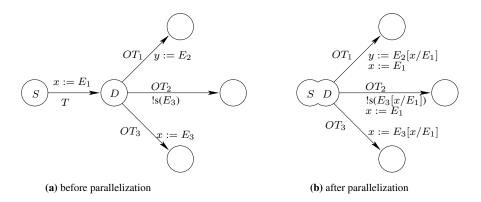

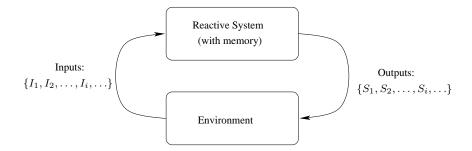

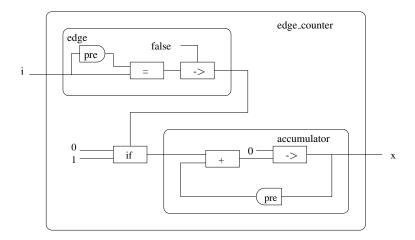

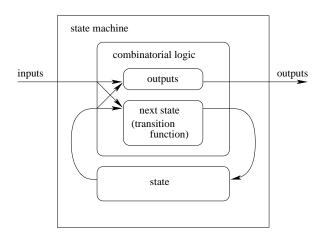

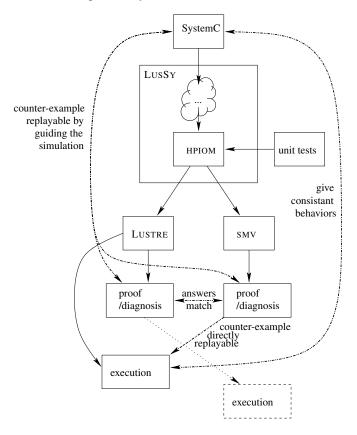

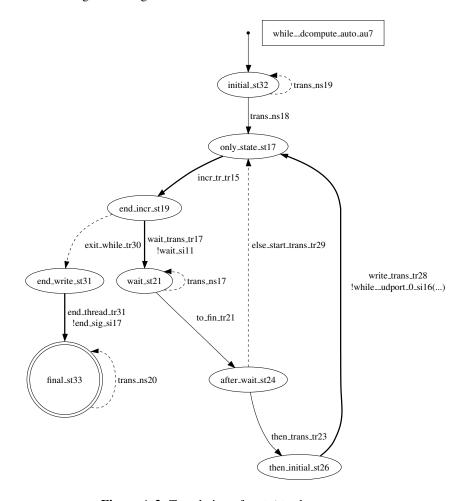

At this level, the architecture of the model must correspond to the one of the actual platform. Each data-transfer in the RTL model must correspond to a transaction of the same size in the PVT model.